#### US010115645B1

# (12) United States Patent Spory

### (10) Patent No.: US 10,115,645 B1

(45) Date of Patent: \*Oct. 30, 2018

# (54) REPACKAGED RECONDITIONED DIE METHOD AND ASSEMBLY

# (71) Applicant: Erick Merle Spory, Colorado Springs, CO (US)

# Inventor: Erick Merle Spory Colorado Springs

# (72) Inventor: **Erick Merle Spory**, Colorado Springs, CO (US)

### (73) Assignee: Global Circuit Innovations, Inc.,

## Colorado Springs, CO (US)

### (\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

This patent is subject to a terminal dis-

claimer.

#### (21) Appl. No.: 15/865,328

#### (22) Filed: Jan. 9, 2018

| (51) | Int. Cl.   |             |

|------|------------|-------------|

|      | H01L 21/48 | (2006.01)   |

|      | H01L 21/02 | (2006.01)   |

|      | H01L 23/26 | (2006.01)   |

|      | H01L 23/10 | (2006.01)   |

|      | H01L 23/20 | (2006.01)   |

|      |            | (Continued) |

#### (52) U.S. Cl.

CPC ....... H01L 23/26 (2013.01); H01L 21/4803 (2013.01); H01L 23/10 (2013.01); H01L 23/20 (2013.01); H01L 23/49513 (2013.01); H01L 23/49838 (2013.01); H01L 24/03 (2013.01); H01L 24/83 (2013.01); H01L 24/85 (2013.01); H01L 24/98 (2013.01); H01L 2224/838 (2013.01)

#### (58) Field of Classification Search

CPC ....... H01L 21/485; H01L 21/4853; H01L 21/4864; H01L 21/4875; H01L 21/4889; H01L 21/4892; H01L 21/02079

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 3,969,813 A * | 7/1976 | Minetti | H05K 13/0486          |  |  |

|---------------|--------|---------|-----------------------|--|--|

| 4.012.832 A * | 3/1977 | Crane   | 156/765<br>H01L 24/32 |  |  |

| , ,           |        |         | 252/514               |  |  |

| (Continued)   |        |         |                       |  |  |

#### FOREIGN PATENT DOCUMENTS

WO WO2011-101262 A1 8/2011

#### OTHER PUBLICATIONS

Getters—molecular scavengers for packaging, Dr. Ken Gilleo and Steve Corbett, HDI Jan. 2001, www.hdi-online.com, 4 pages.

(Continued)

Primary Examiner — David A Zarneke (74) Attorney, Agent, or Firm — Thomas J. Lavan

#### (57) ABSTRACT

A method is provided. The method includes one or more of removing one or more existing ball bonds from an extracted die, reconditioning die pads of the extracted die to create a reconditioned die, securing the reconditioned die within a cavity of a new package base, providing a plurality of bond connections interconnecting the reconditioned die pads and package leads or downbonds of the new package base, applying an encapsulating compound over the reconditioned die and the plurality of bond connections to create an assembled package base, and securing a lid to the new package base. Reconditioning includes applying a plurality of metallic layers to the die pads of the extracted die, the extracted die including a fully functional semiconductor die removed from a previous package. The encapsulating compound is configured to exhibit low thermal expansion.

#### 20 Claims, 18 Drawing Sheets

| (51) Int. Cl.  H01L 23/495  H01L 23/00  H01L 23/498                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | (2006.01)<br>(2006.01)<br>(2006.01)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2014/0252584 A1 9/2014 Spory<br>2016/0181168 A1 6/2016 Spory<br>2016/0181171 A1 6/2016 Spory<br>2016/0225686 A1 8/2016 Spory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (56) <b>Re</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | eferences Cited                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | OTHER PUBLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| U.S. PATERION U. | ### Cited  FENT DOCUMENTS  /1984 Grabbe /1986 Frampton /1991 Nishiguchi /1993 Satoh /1993 Hamburgen et al. /1996 Bergeron /1997 Groover et al. /1998 Galloway /1998 Wills /1999 Fisher et al. /2000 Mizuno et al. /2000 Mizuno et al. /2001 Manning /2002 Young                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Cookson Group Staydry SD1000 High Temperature Moisture Getter data sheet, Cookson Group, May 30, 2011, 1 page.  Wikipdia "Getter", retrieved May 30, 2011, http://en.wikipedia.org/wiki/Getter.  Wikipdia "Kirkendall effect", retrieved Jul. 5, 2011, http://en.wikipedia.org/wiki/Kirkendall effect.  Flip Chips dot com, Tutorial 72—Mar. 2007, Redistribution Layers, article by George A. Riley, PhD, Flipchips dot com website, downloaded Dec. 18, 2011: http://www.flipchips.com/tutorial72.html.  MIT article "Liquid Metal Printer Lays Electronic Circuits on Paper, Plastic, and even Cotton", downloaded from MIT Technology Review Nov. 22, 2013, http://www.technologyreview.com/view/521871/liquid-metal-printer-lays-electronic-circuits-on-paper-plastic-and-even-cotton/.  sPRO 125 and sPRO 250 Direct Metal SLM Production Printer datasheet, 3DSystems, Part No. 70743, Issue Date Apr. 10, 2012. Wikipedia "3D Printing" reference, downloaded Jan. 12, 2015. Wikipedia "Ball Bonding", downloaded Apr. 11, 2016. Solid State Technology "The back-end process: Step 7—Solder bumping step by step", by Deborah S. Patterson, http://electroiq.com/blog/2001/07/the-back-end-process-step-7-solder-bumping-step-by-step/, downloaded Apr. 11, 2016.  Official Action for U.S. Appl. No. 13/623,603, dated Dec. 9, 2014. Official Action for U.S. Appl. No. 13/623,603, dated Aug. 14, 2015.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2002/0084528 A1 7, 2002/0182782 A1 12, 2003/0127423 A1 7, 2004/0006150 A1 1, 2004/0040855 A1 3, 2005/0057883 A1 2005/0085578 A1 4, 2005/0285250 A1 12, 2006/0166406 A1 7, 2007/0207661 A1 1, 2007/0259470 A1 11, 2007/0259470 A1 11, 2007/0295456 A1 12, 2008/0124547 A1 5, 2008/0124547 A1 5, 2008/0124547 A1 5, 2008/0124547 A1 5, 2009/0151972 A1 6, 2009/0160047 A1 2009/0160047 A1 2009/0160047 A1 2010/0079035 A1 4, 2010/0200262 A1 8, 2010/0246152 A1 2010/0246152 A1 2011/0215449 A1  | Ahiko et al.   Ahik | Official Action for U.S. Appl. No. 13/623,603, dated Apr. 29, 2016. Official Action for U.S. Appl. No. 13/623,603, dated Aug. 24, 2016. Official Action for U.S. Appl. No. 13/623,603, dated Apr. 11, 2017. Official Action for U.S. Appl. No. 13/785,959, dated Jan. 5, 2015. Official Action for U.S. Appl. No. 13/785,959, dated Jan. 5, 2015. Official Action for U.S. Appl. No. 14/142,823, dated Jan. 5, 2015. Official Action for U.S. Appl. No. 14/142,823, dated May 11, 2015. Official Action for U.S. Appl. No. 14/142,823, dated Oct. 9, 2015. Official Action for U.S. Appl. No. 14/142,823, dated Feb. 29, 2016. Official Action for U.S. Appl. No. 14/142,823, dated Jul. 28, 2016. Official Action for U.S. Appl. No. 14/142,823, dated Jul. 28, 2016. Official Action for U.S. Appl. No. 14/655,626, dated Aug. 28, 2015. Official Action for U.S. Appl. No. 14/600,691, dated Aug. 10, 2015. Official Action for U.S. Appl. No. 14/600,691, dated Feb. 19, 2016. Official Action for U.S. Appl. No. 14/600,691, dated Jul. 29, 2016. Official Action for U.S. Appl. No. 14/600,691, dated Dec. 27, 2016. Notice of Allowance for U.S. Appl. No. 14/600,733, dated Apr. 17, 2015. Official Action for U.S. Appl. No. 14/600,733, dated Apr. 17, 2015. Official Action for U.S. Appl. No. 14/600,733, dated May 9, 2016. Official Action for U.S. Appl. No. 14/600,733, dated May 9, 2016. Official Action for U.S. Appl. No. 14/600,733, dated May 9, 2016. Official Action for U.S. Appl. No. 14/600,733, dated May 2, 2016. Official Action for U.S. Appl. No. 14/600,733, dated May 9, 2016. Official Action for U.S. Appl. No. 14/600,733, dated May 9, 2016. Official Action for U.S. Appl. No. 14/600,733, dated May 9, 2016. Official Action for U.S. Appl. No. 14/600,733, dated May 2, 2016. Official Action for U.S. Appl. No. 14/600,733, dated May 2, 2016. Official Action for U.S. Appl. No. 14/600,733, dated May 2, 2016. Official Action for U.S. Appl. No. 14/600,733, dated May 2, 2016. Official Action for U.S. Appl. No. 15/088,822, dated Mar. 24, 2017. Notice of Allowance for U.S. |

Fig. 1 Bare Die with Die Pads

Fig. 2 Extracted Die with Bond Pads, Ball Bonds, and Bond Wires

Fig. 3B Modified Extracted Die Section A-A After Original Ball Bond and Original Bond Wire Removal

Fig. 3C Electroless Nickel Layer Application Section A-A

Fig. 3D Electroless Palladium Layer Section A-A

Fig. 3E Immersion Gold Layer Application Section A-A

Fig. 3F Reconditioned Die after New Ball Bonding Section A-A

Fig. 3H Reconditioned Die after 3D Printing Process Section A-A

404 Package Base

Fig. 4B Rebonded Reconditioned Die with New Bond Wires

412 Die Attach Adhesive

Fig. 4C Rebonded and Encapsulated Reconditioned Die

Fig. 4D Repackaged Integrated Circuit

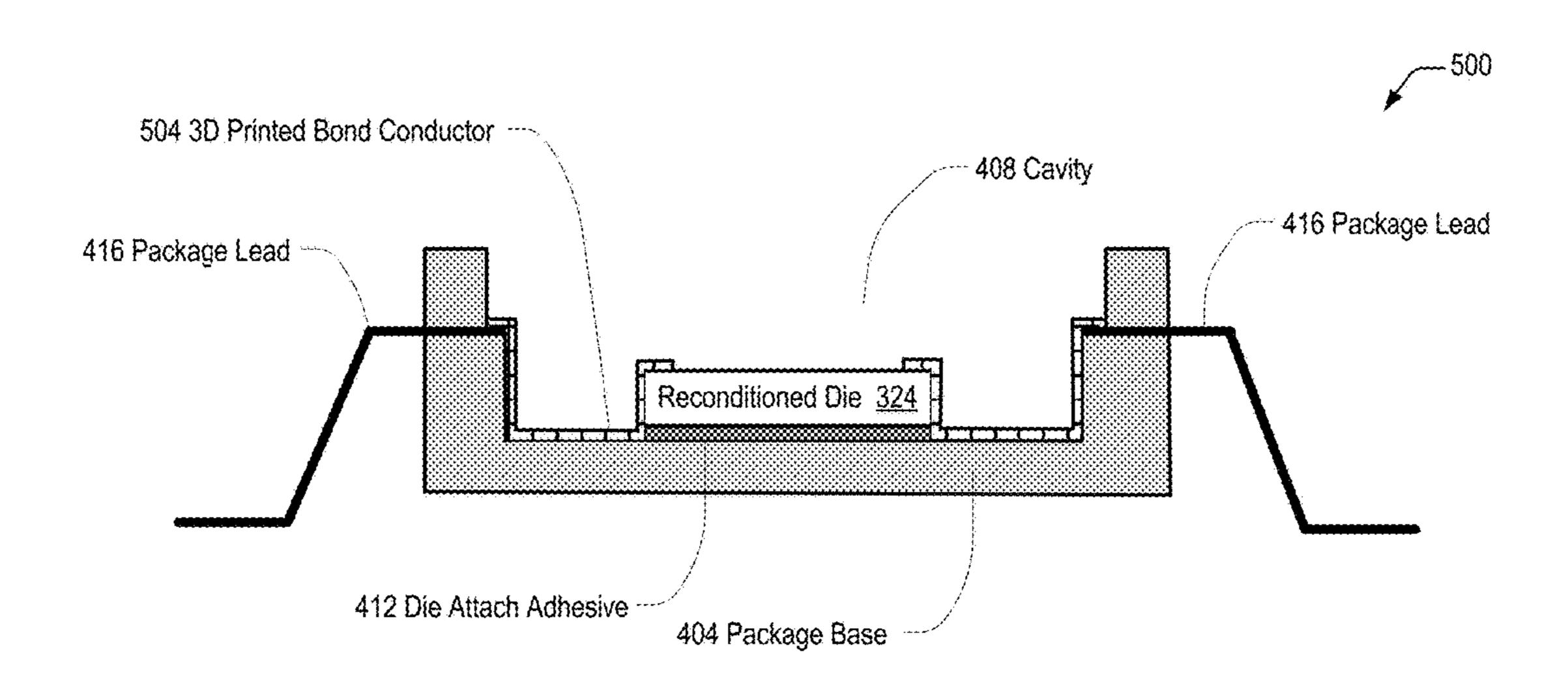

Fig. 5A Rebonded Reconditioned Die with 3D Printed Bond Conductors

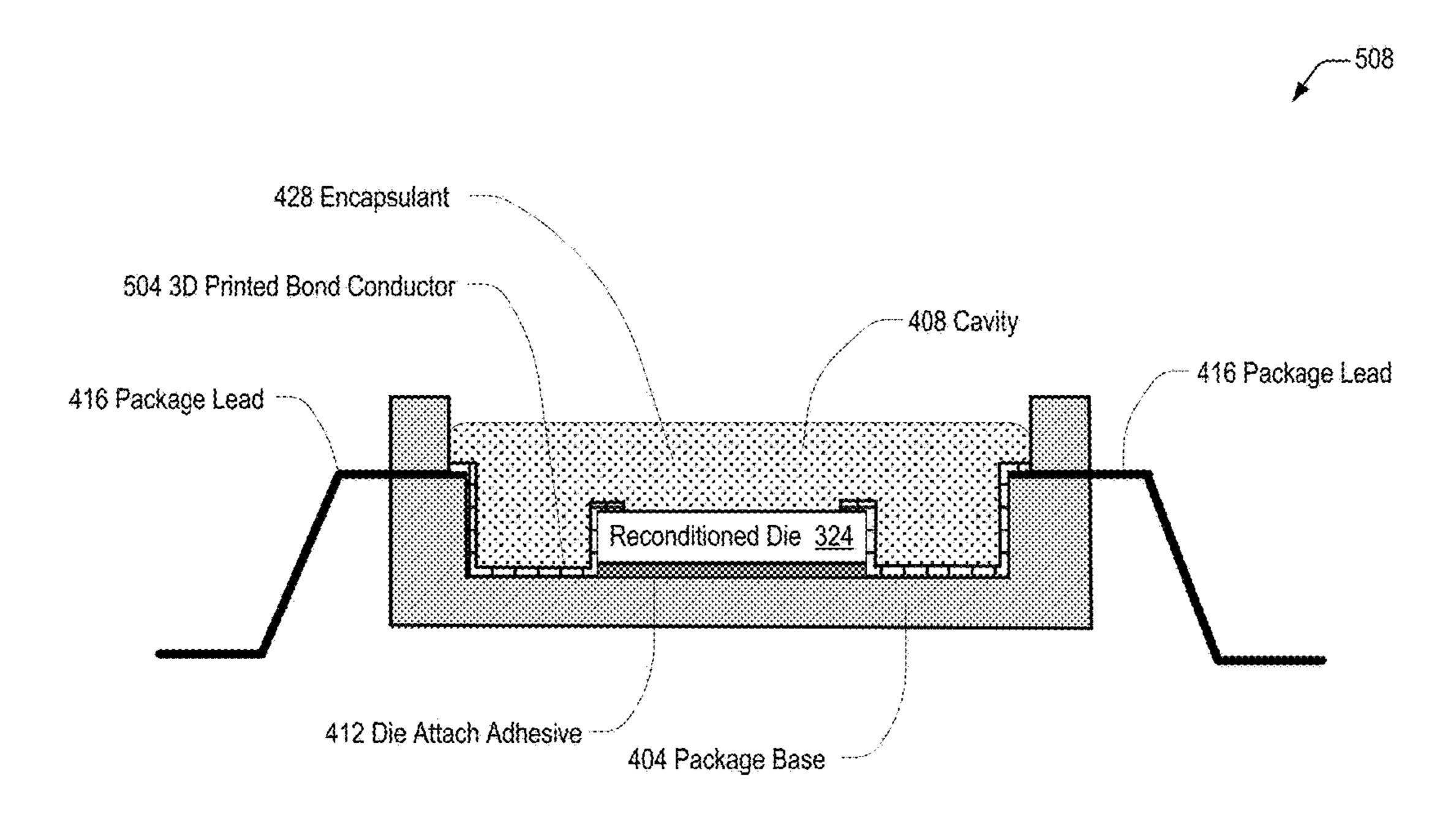

Fig. 5B Rebonded and Encapsulated Reconditioned Die

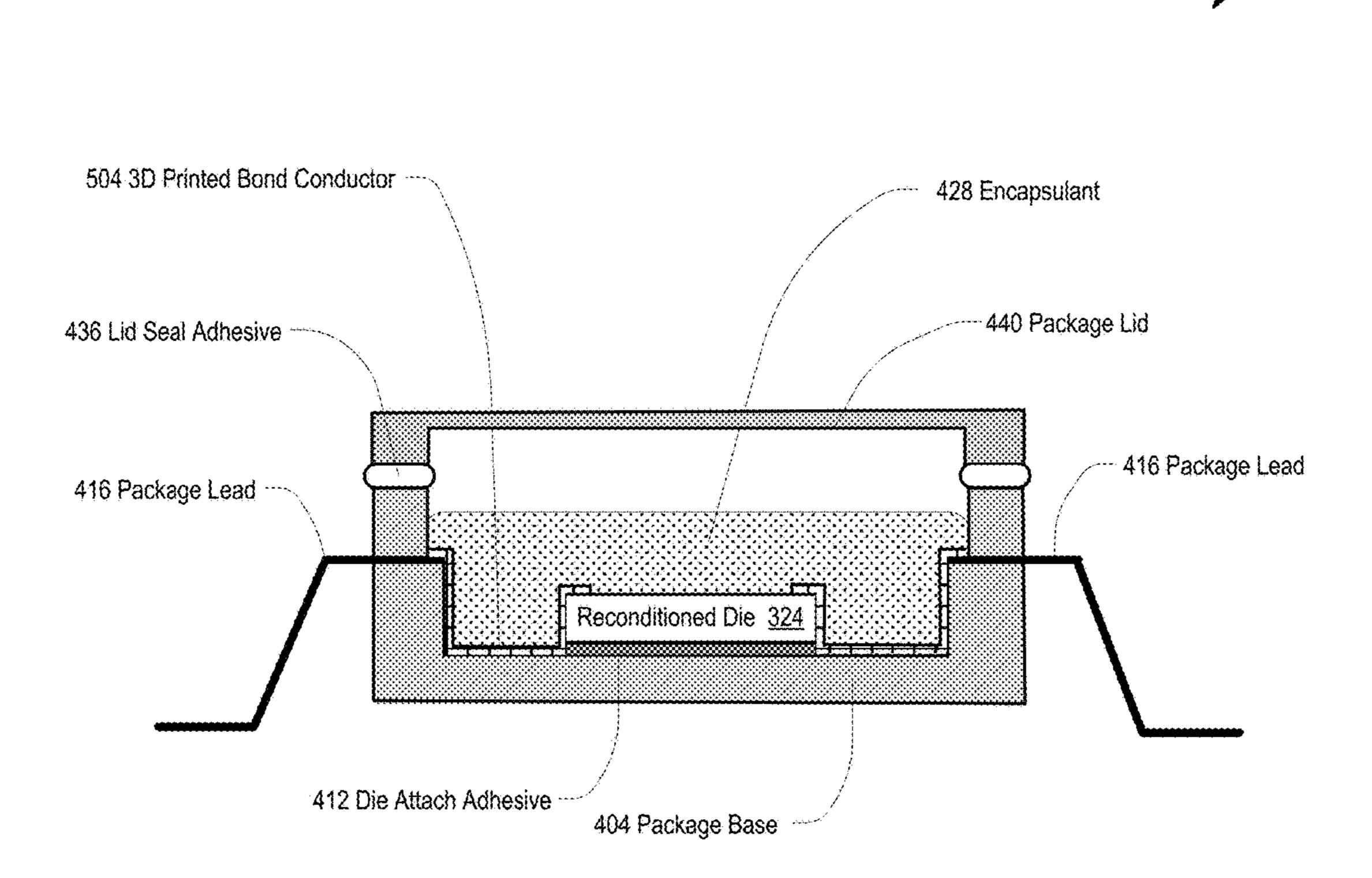

Fig. 5C Repackaged Integrated Circuit

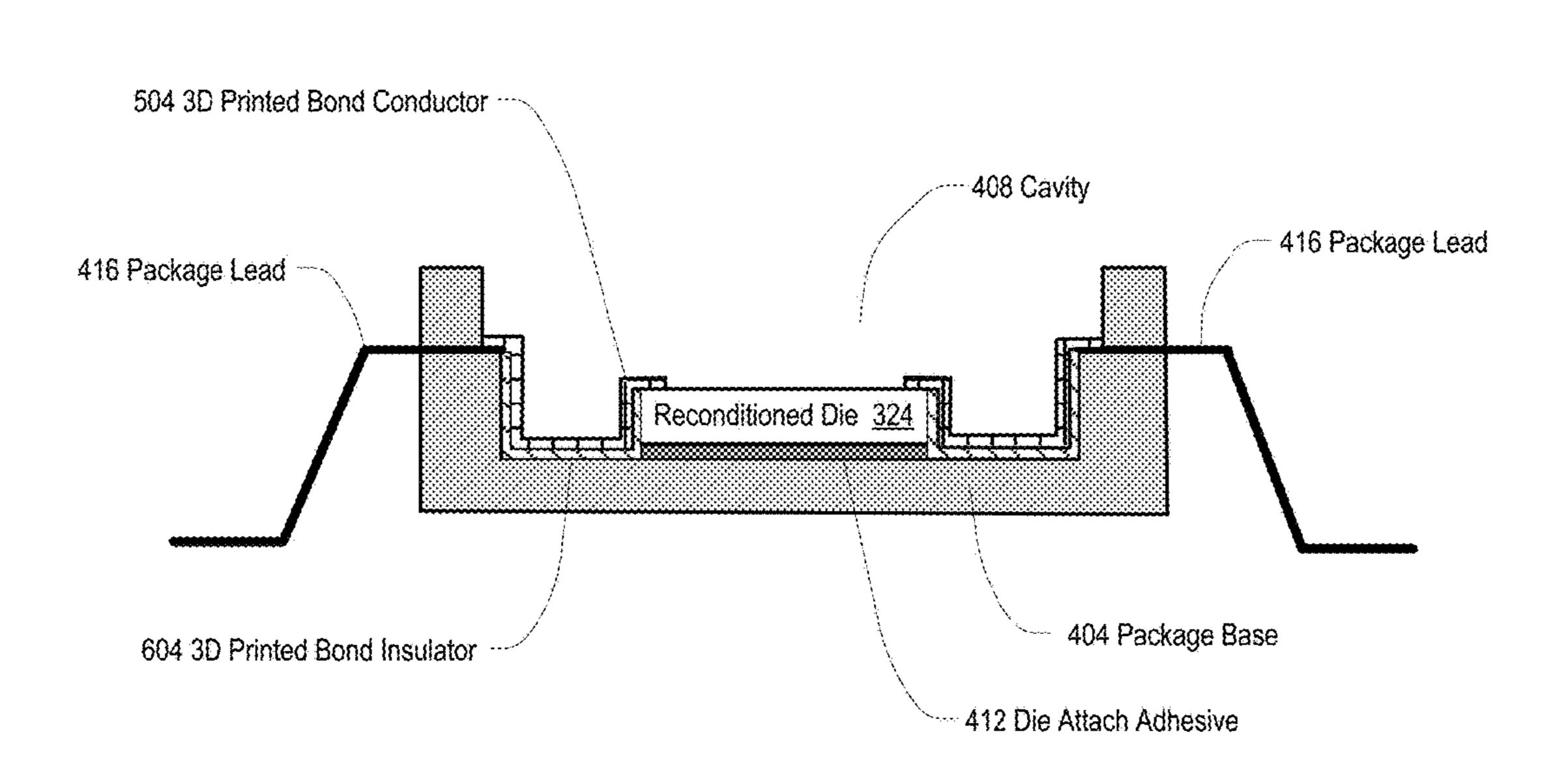

Fig. 6A Rebonded Reconditioned Die with 3D Printed Bond Insulators

Fig. 6B Rebonded Reconditioned Die with 3D Printed Bond Conductors over 3D Printed Bond Insulators

Fig. 6C Rebonded and Encapsulated Reconditioned Die

Fig. 6D Repackaged Integrated Circuit

Fig. 7A Reconditioning Process for Extracted Die

Fig. 7B Reconditioning Process for Extracted Die

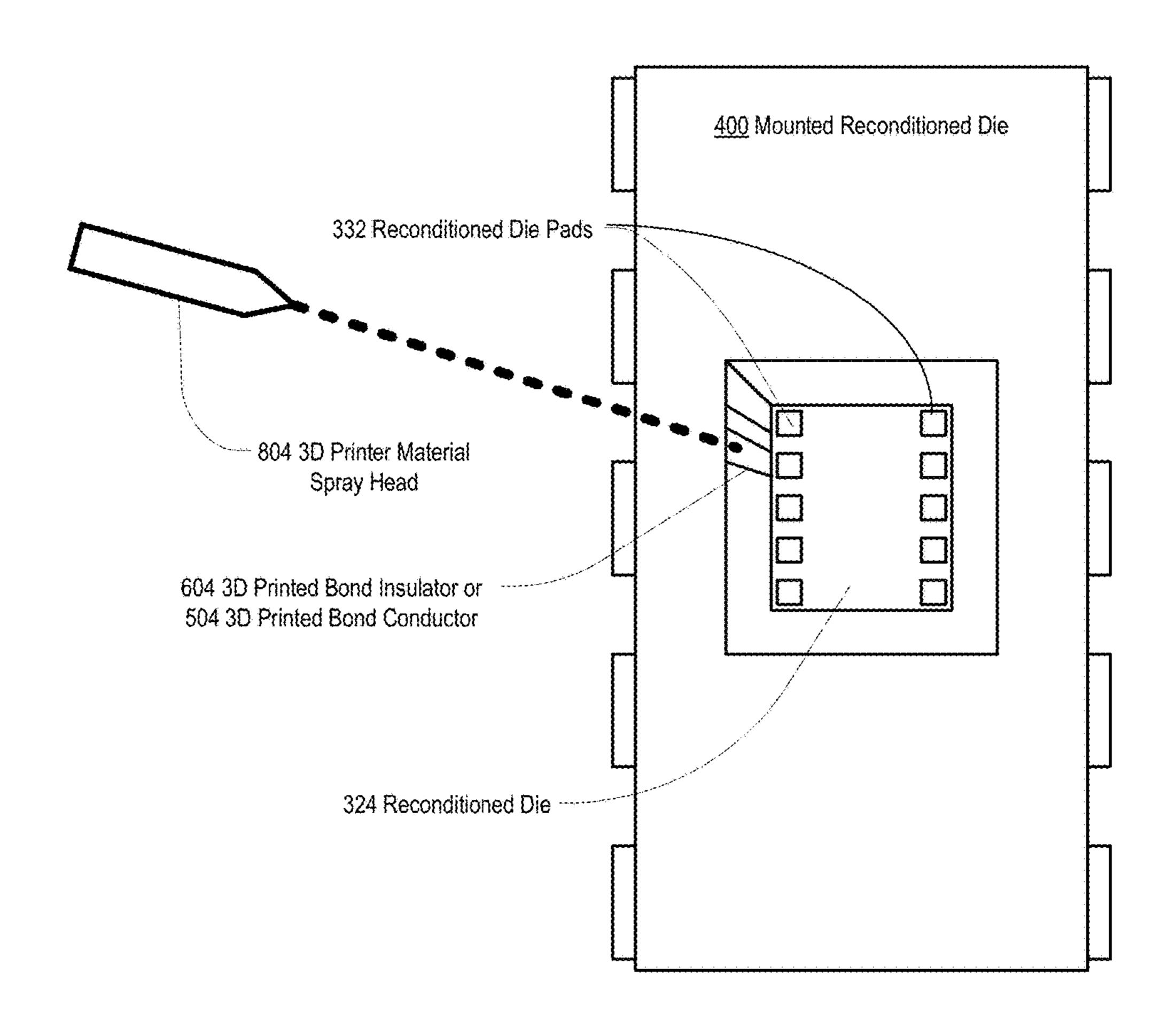

Fig. 8 Apply Insulating and Conducting Material Spray with 3D Printer

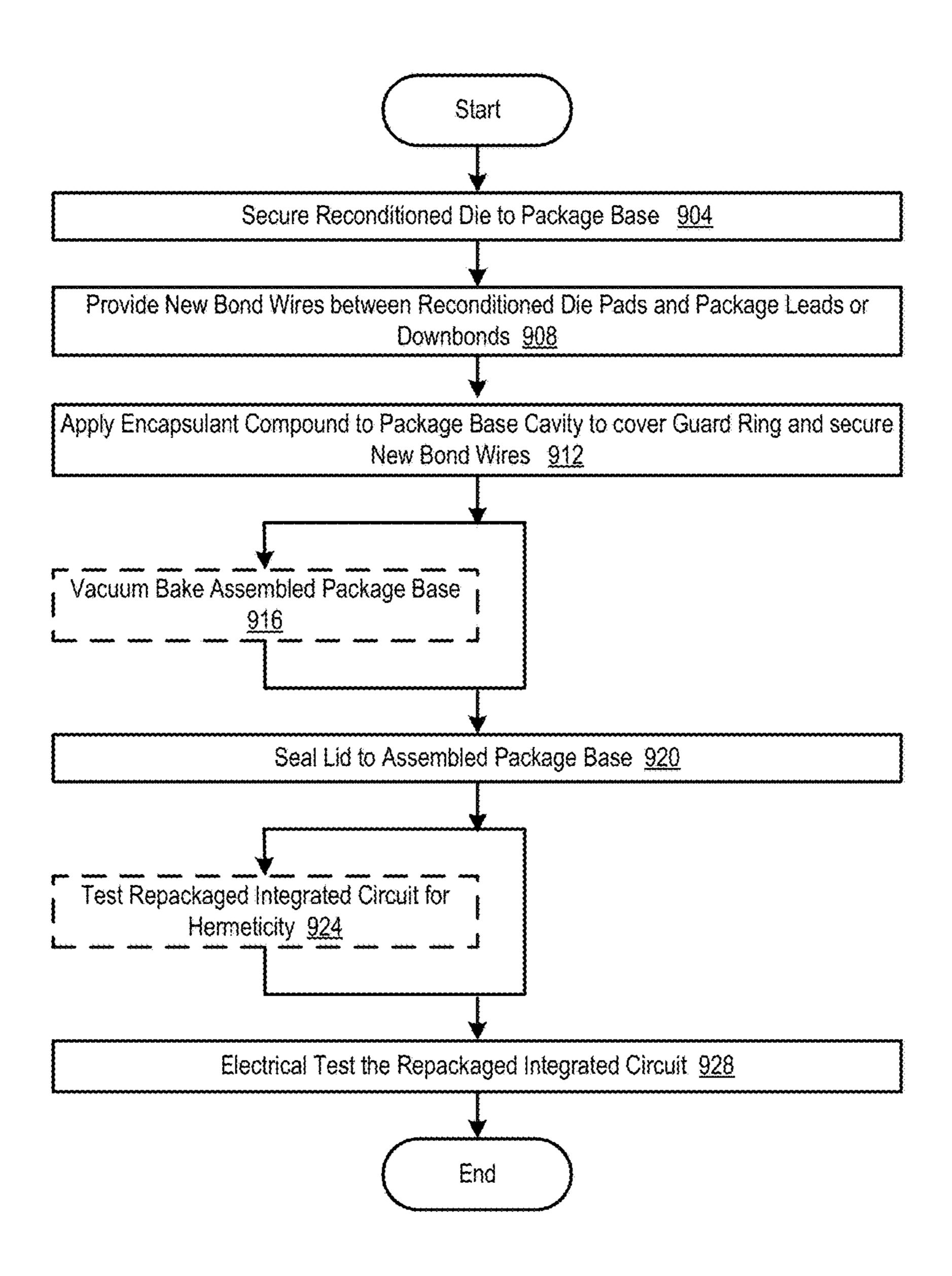

Fig. 9A Assembly Process for Repackaged Reconditioned Die

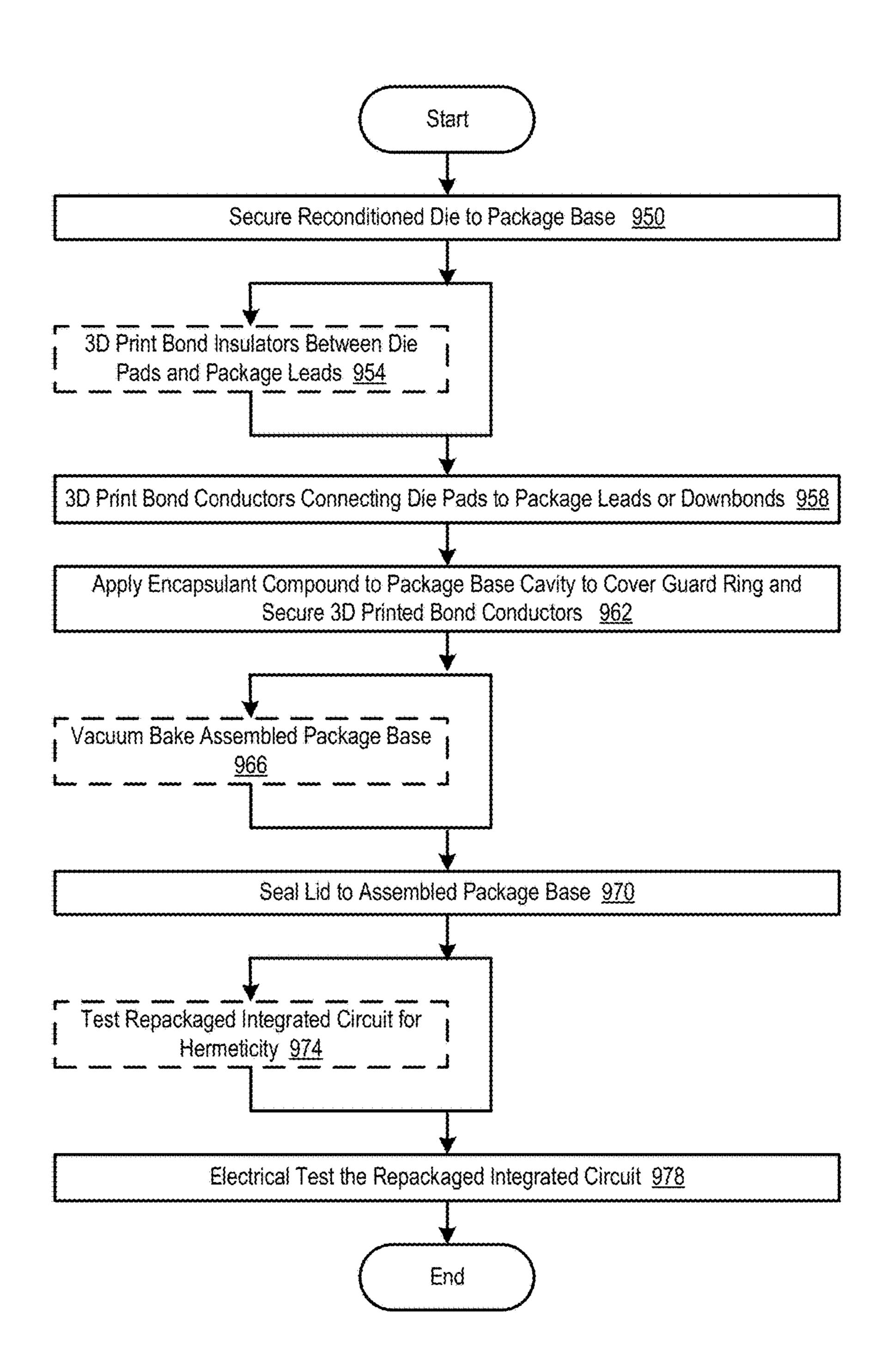

Fig. 9B Assembly Process for Repackaged Reconditioned Die

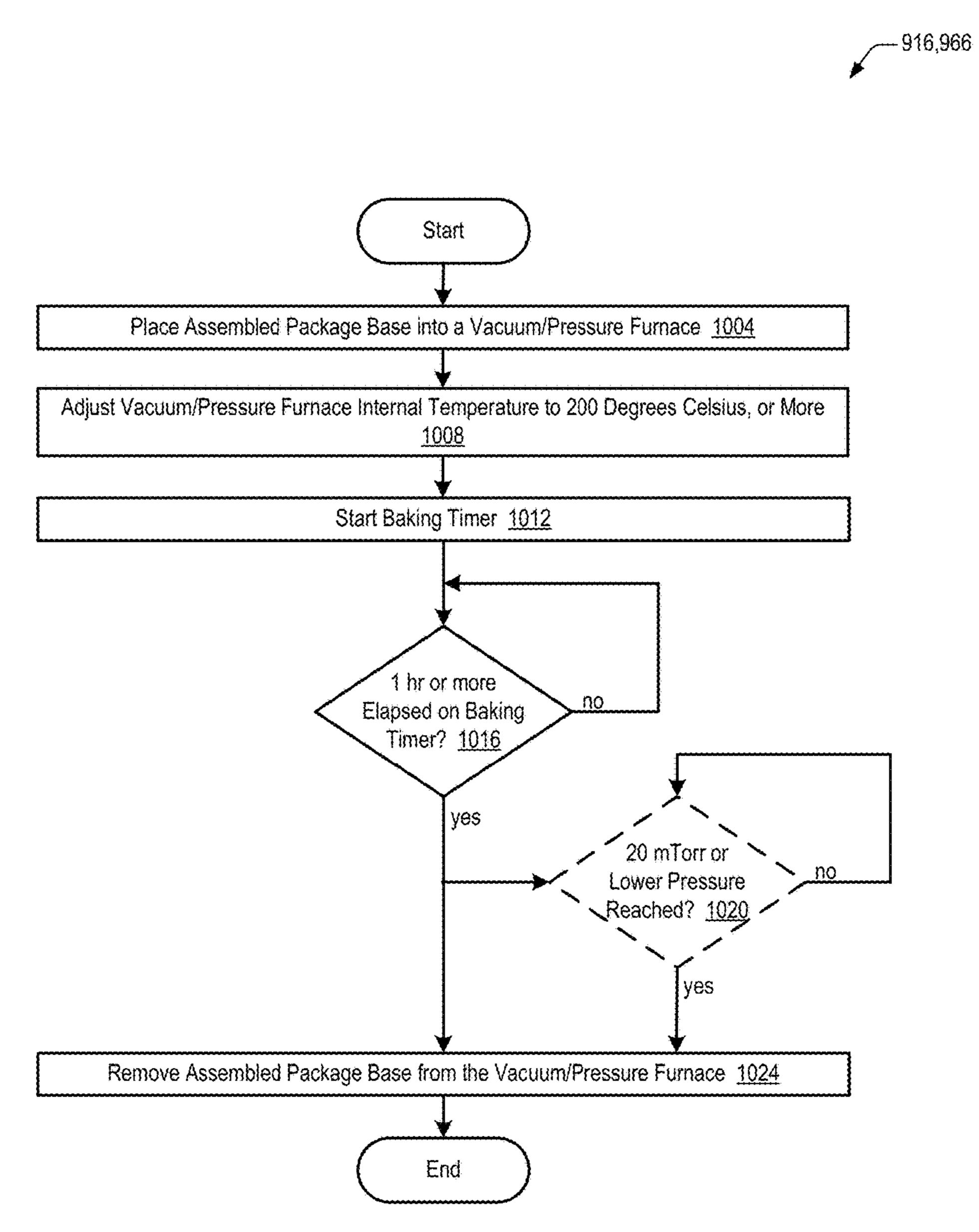

Fig. 10 Vacuum Bake Process

#### REPACKAGED RECONDITIONED DIE METHOD AND ASSEMBLY

#### **FIELD**

The present invention is directed to integrated circuit packaging. In particular, the present invention is directed to methods and apparatuses for creating repackaged integrated circuits capable of operating at extended temperatures over extended lifetimes.

#### BACKGROUND

Integrated circuits are available in many different packages, technologies, and sizes. Most integrated circuits are 15 available in plastic packages, which are generally intended for commercial operating environments at a low cost. Commercial operating environments have a specified operating range from 0° C. to 70° C. Integrated circuits for military applications have historically been packaged in either metal 20 or ceramic hermetic packages, which are able to work reliably in more demanding environments than commercial integrated circuits. Military operating environments have a specified operating range from -55° C. to 125° C. In order to save costs, the military has purchased integrated circuits 25 through COTS (Commercial Off-The-Shelf) programs. However, these components are generally commercial grade components in plastic packages, and not intended for demanding environments requiring the broader temperature range reliability and durability of ceramic and metal her- 30 metically packaged integrated circuits.

Depending on size and complexity, integrated circuits are available in a wide range of packages. Although many older integrated circuits were packaged using through-hole technology packages, surface mount packages have dominated over the past several decades. Surface mount packages generally have circuit density, cost, and other advantages over through-hole integrated circuits. Examples of through-hole packages include DIP (dual-in-line plastic) and PGA (pin grid array). Examples of surface mount packages include SOIC (small-outline integrated circuit) and PLCC (plastic leaded chip carrier).

In many cases, products requiring integrated circuits are in production or service for a longer time period than the manufacturing lifetime of a given integrated circuit. In such 45 cases, it is not uncommon for parts to become obsolete or become unable to be purchased. For example, in a typical month, about 3% of all packaged integrated circuit product types become obsolete. One mitigating approach to this issue is to buy a sufficient lifetime inventory of spares for 50 integrated circuits that are likely to become obsolete at a future date. However, this may be costly if a large quantity of integrated circuits needs to be purchased as spares. It also may result in far more spares being purchased that are actually required, since projected future needs may only be 55 a rough estimate. When spares are needed in the future when an IC is no longer in active production, the ICs that are actually available may be in a different package than is required, since popular ICs are typically offered in multiple package options. For example, spares may be available in 60 plastic DIP packages while the using assemblies require SOIC packages.

#### **SUMMARY**

The present invention is directed to solving disadvantages of the prior art. In accordance with embodiments of the

2

present invention, a method is provided. The method includes one or more of removing one or more existing ball bonds from an extracted die, reconditioning die pads of the extracted die to create a reconditioned die, securing the reconditioned die within a cavity of a new package base, providing a plurality of bond connections interconnecting the reconditioned die pads and package leads or downbonds of the new package base, applying an encapsulating compound over the reconditioned die and the plurality of bond 10 connections to create an assembled package base, and securing a lid to the new package base. Reconditioning includes applying a plurality of metallic layers to the die pads of the extracted die, the extracted die including a fully functional semiconductor die removed from a previous package. The encapsulating compound is configured to exhibit low thermal expansion.

In accordance with another embodiment of the present invention, a packaged integrated circuit is provided. The packaged integrated circuit includes a reconditioned die, a new package base including package leads and a cavity, a plurality of bond connections interconnecting reconditioned die pads and the package leads or downbonds of the new package base, an encapsulating compound applied over the reconditioned die and the plurality of bond connections to create an assembled package base, and a lid, secured to the assembled package base. The reconditioned die is secured within the cavity, and includes an extracted die with original ball bonds removed, and reconditioned die pads. The extracted die includes a fully functional semiconductor die including original ball bonds and removed from a previous package. Reconditioned die pads include a plurality of metallic layers applied to die pads of the extracted die. The encapsulating compound is configured to exhibit low thermal expansion.

An advantage of the present invention is that it provides an improved packaged integrated circuit that works reliably at extended temperatures, without requiring moisture getters or inert gases within a new integrated circuit package. The present invention utilizes reconditioned die pads to eliminate bonding interconnection reliability problems that may occur with dissimilar metals, and specifically with Gold-Aluminum interfaces. By eliminating processing steps with moisture getters and inert gases, a lower cost repackaged integrated circuit is achieved.

Another advantage of the present invention is it provides a hermetic integrated circuit with improved reliability using older extracted dice, which may no longer be available wither as wafers or as bare dice. By reclaiming extracted dice, removing original ball bonds and bond wires, and reconditioning die pads, a reconditioned die with improved reliability is available to be repackaged into new hermetic packages.

Another advantage of the present invention is it is able to accommodate both conventional wire bonding processes as well as newer 3D printed bond connection processes. Wire bonding is suitable for conventional interconnections to a conventional lead frame, where the die pinout generally matches the package pinout (i.e. not requiring crossed bond wires). 3D printed bond connections are suitable for both conventional and unconventional interconnections. Unconventional interconnections include situations where the die pinout does not match the package pinout, and crossed bond connections are required.

Yet another advantage of the present invention is it 65 provides improved reliability compared to conventional integrated circuits by encapsulating bond interconnections between the reconditioned die and package leads or down-

bonds. Following wire bonding or 3D printing new bond connections, an encapsulant is added to the new package cavity to prevent metallic particles from flaking off and potentially contaminating the packaged integrated circuit and thereby reducing reliability.

Additional features and advantages of embodiments of the present invention will become more readily apparent from the following description, particularly when taken together with the accompanying drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

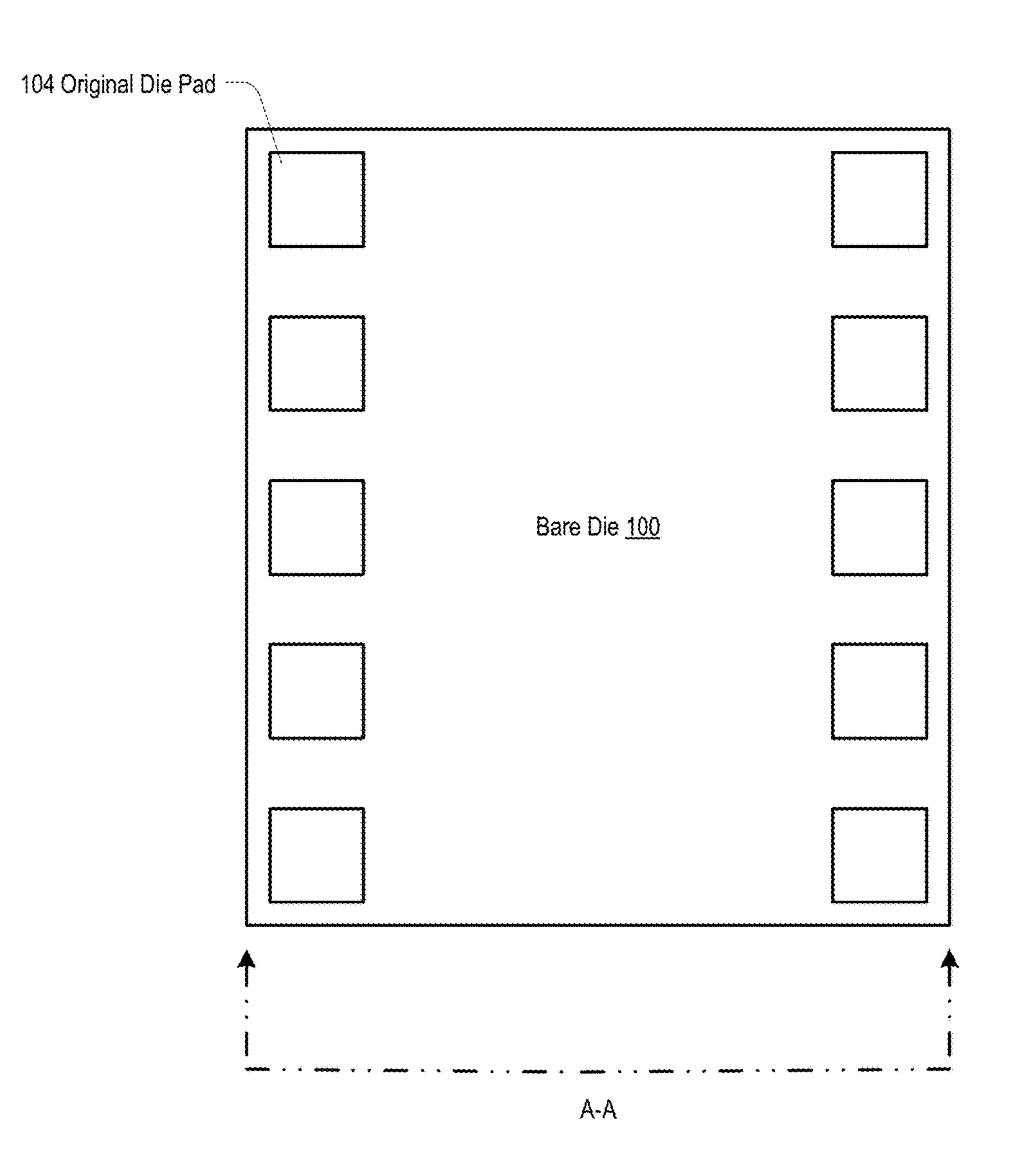

- FIG. 1 is a diagram illustrating a bare die with original die pads in accordance with embodiments of the present invention.

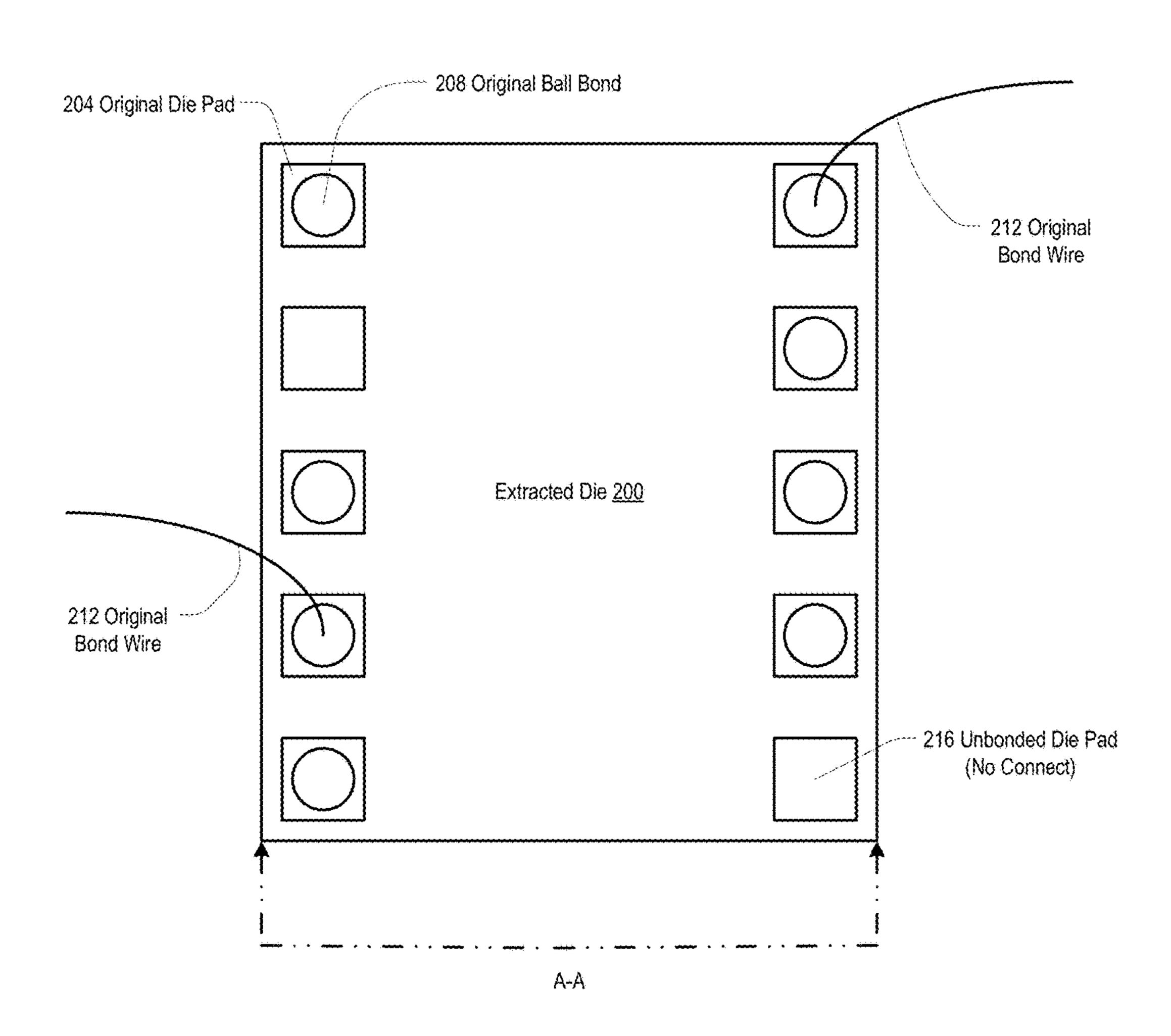

- FIG. 2 is a diagram illustrating an extracted die with die pads, ball bonds, and bond wires in accordance with embodiments of the present invention.

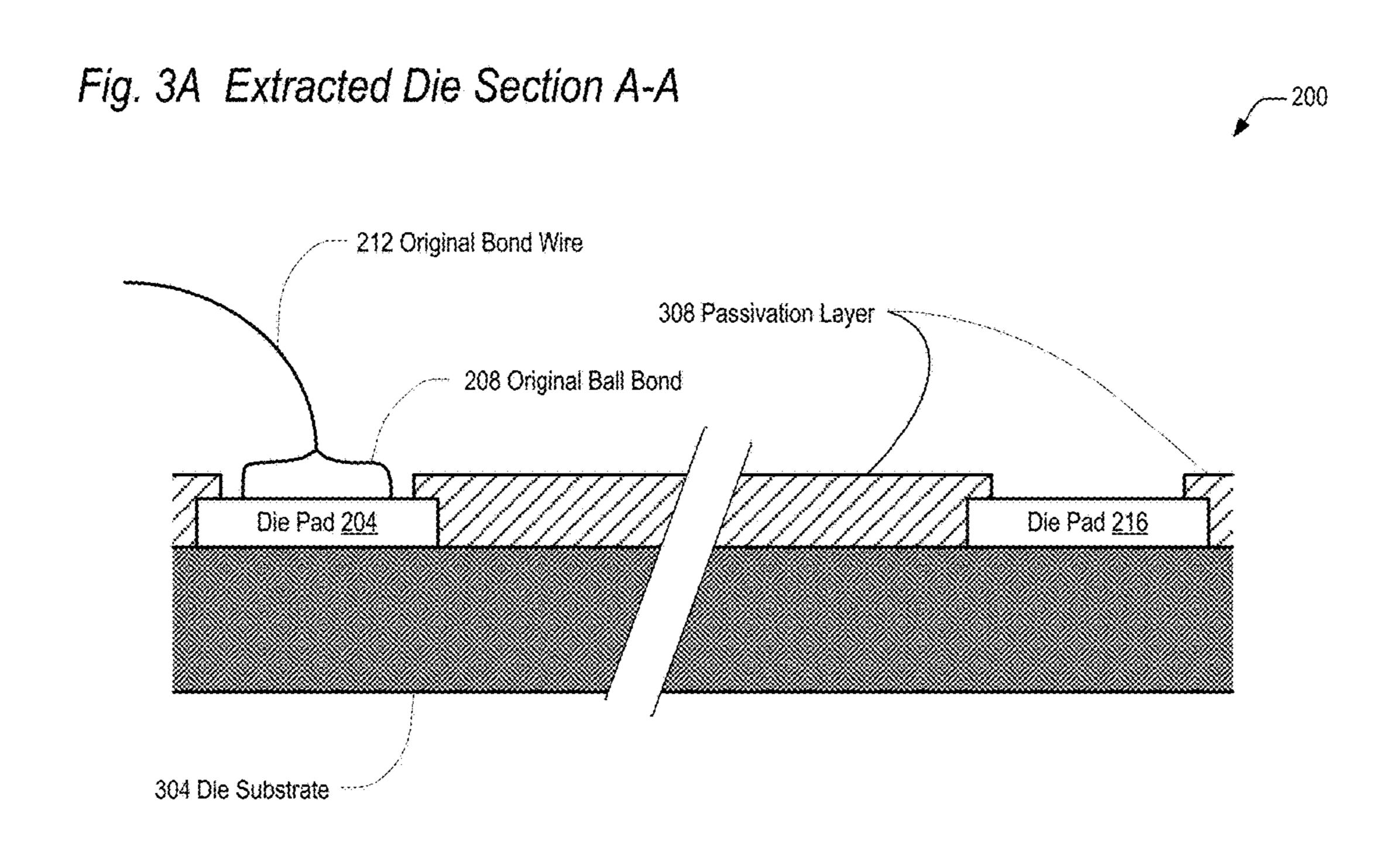

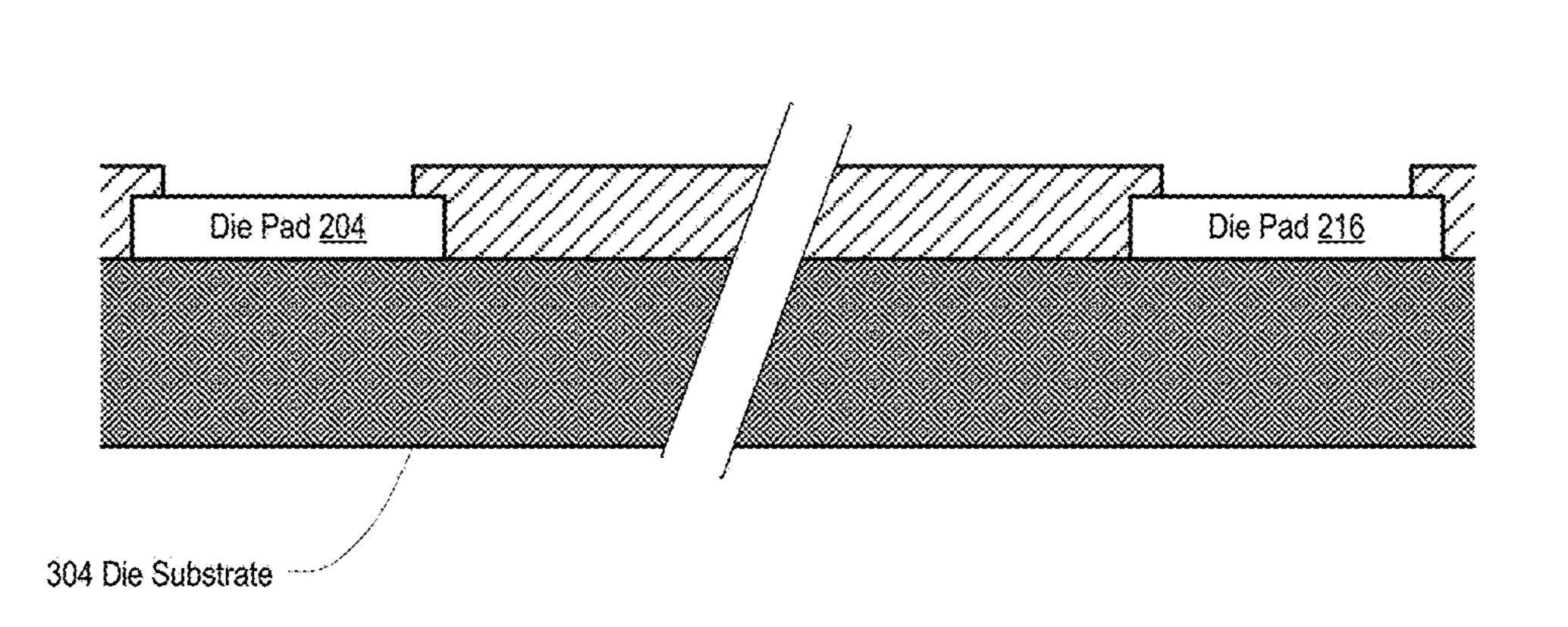

- FIG. 3A is a diagram illustrating a section A-A of an extracted die in accordance with embodiments of the present 20 invention.

- FIG. 3B is a diagram illustrating a section A-A of a modified extracted die after original ball bond and original bond wire removal in accordance with embodiments of the present invention.

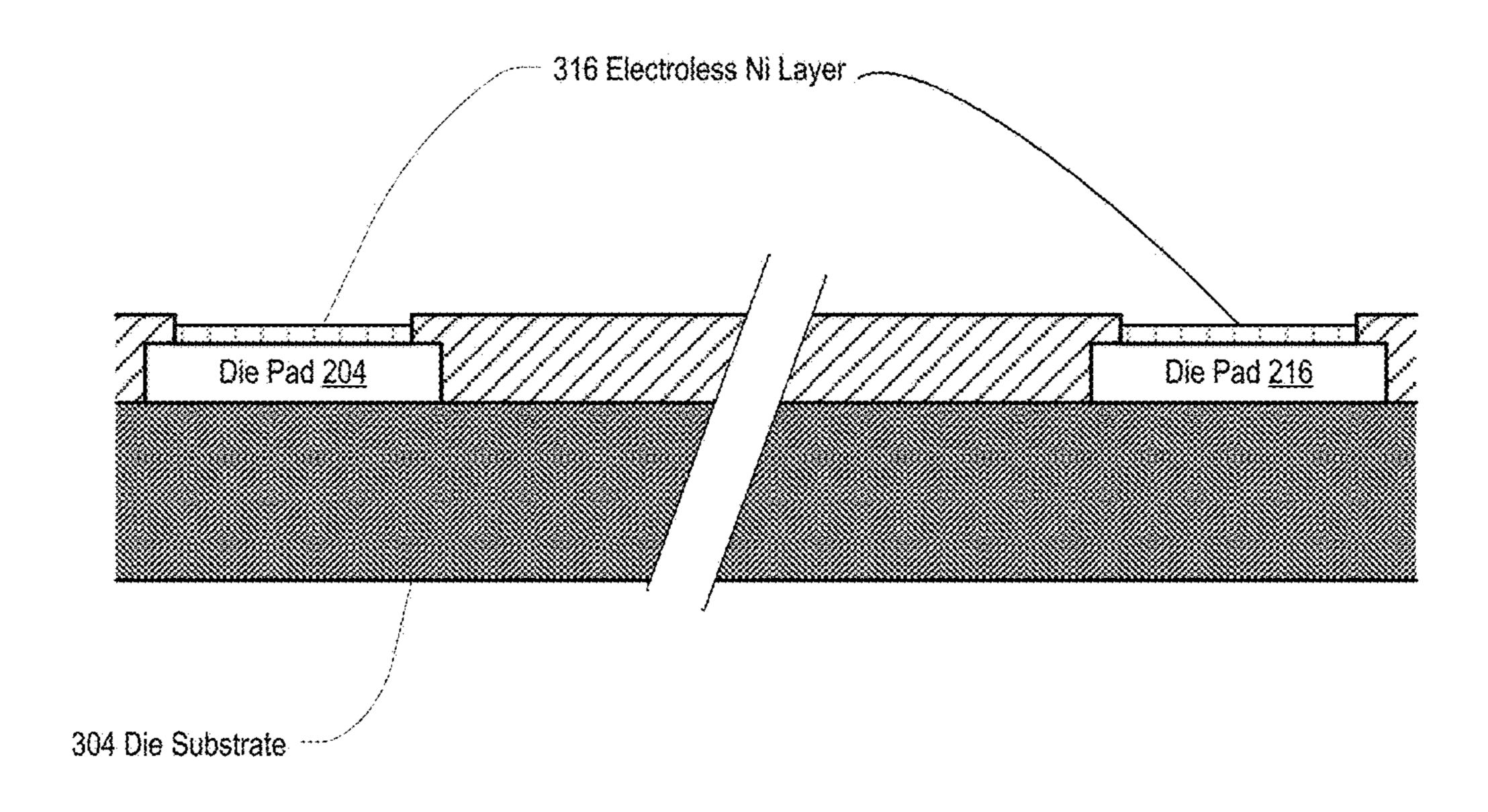

- FIG. 3C is a diagram illustrating a section A-A of electroless Nickel layer application in accordance with embodiments of the present invention.

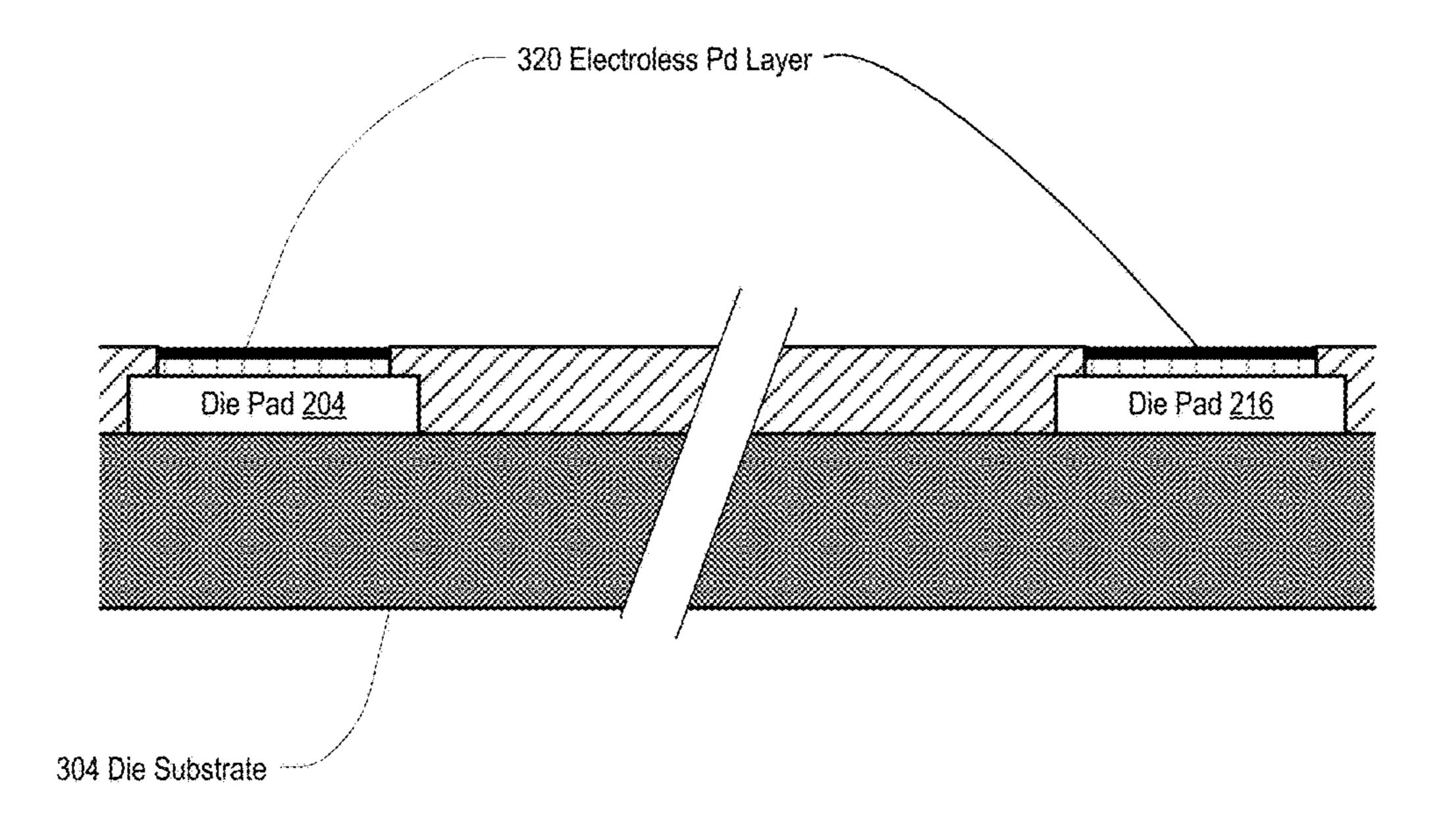

- FIG. 3D is a diagram illustrating a section A-A of electroless Palladium layer application in accordance with 30 embodiments of the present invention.

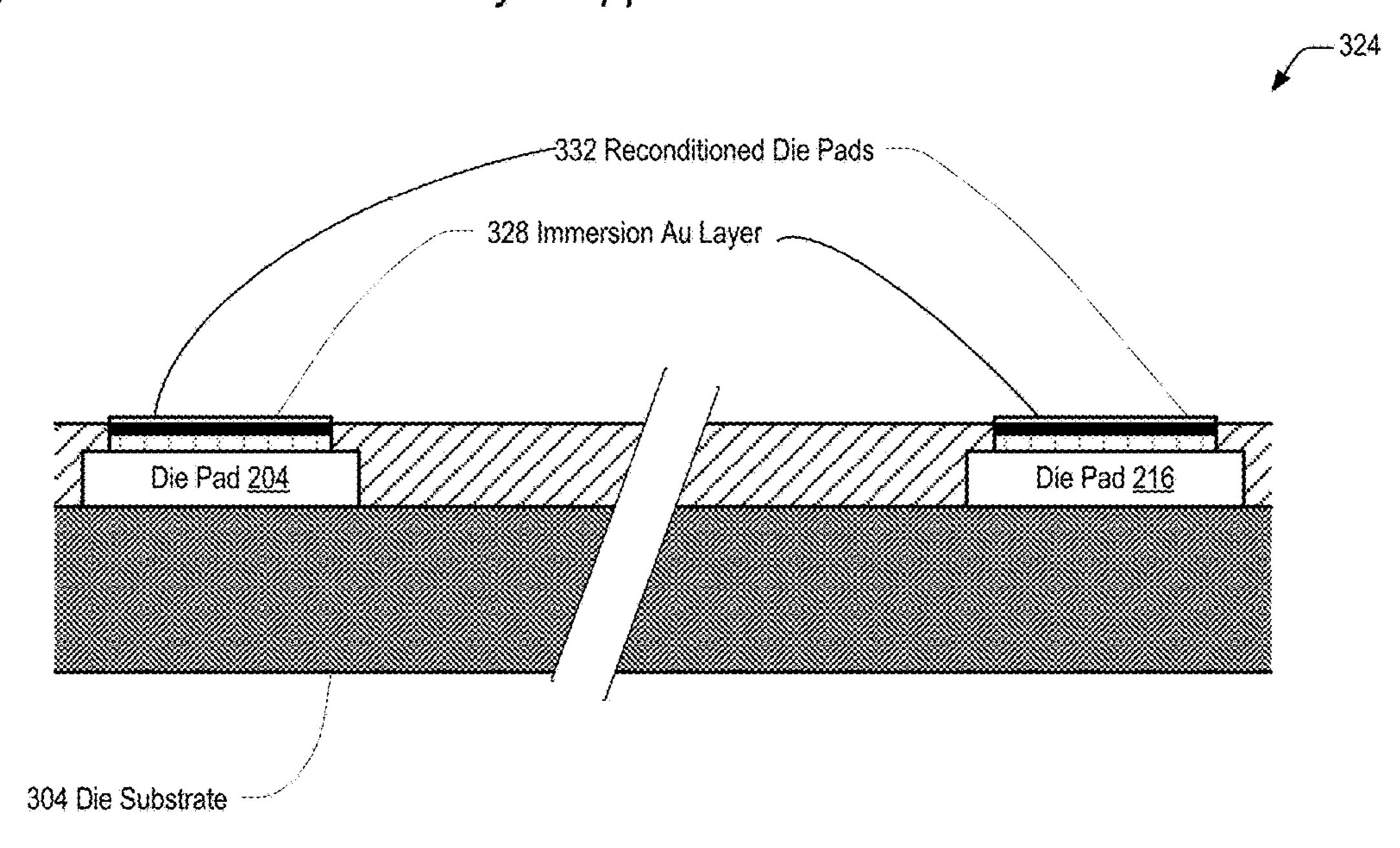

- FIG. 3E is a diagram illustrating a section A-A of immersion Gold layer application in accordance with embodiments of the present invention.

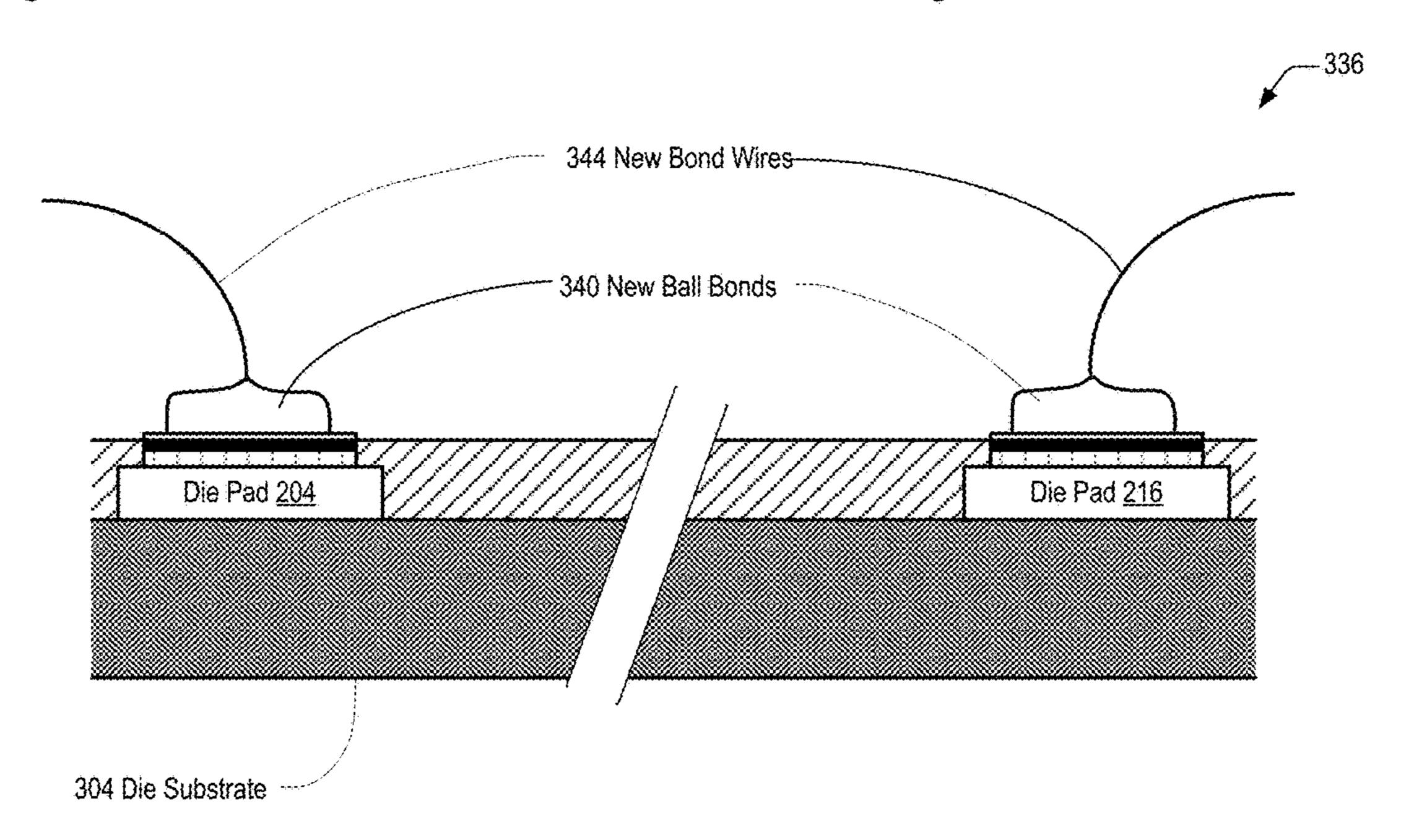

- reconditioned die after a new ball bonding process in accordance with embodiments of the present invention.

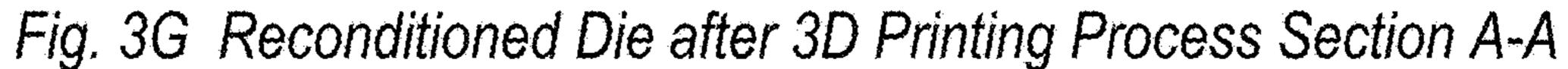

- FIG. 3G is a diagram illustrating a section A-A of a reconditioned die after a 3D printing process in accordance with a first embodiment of the present invention.

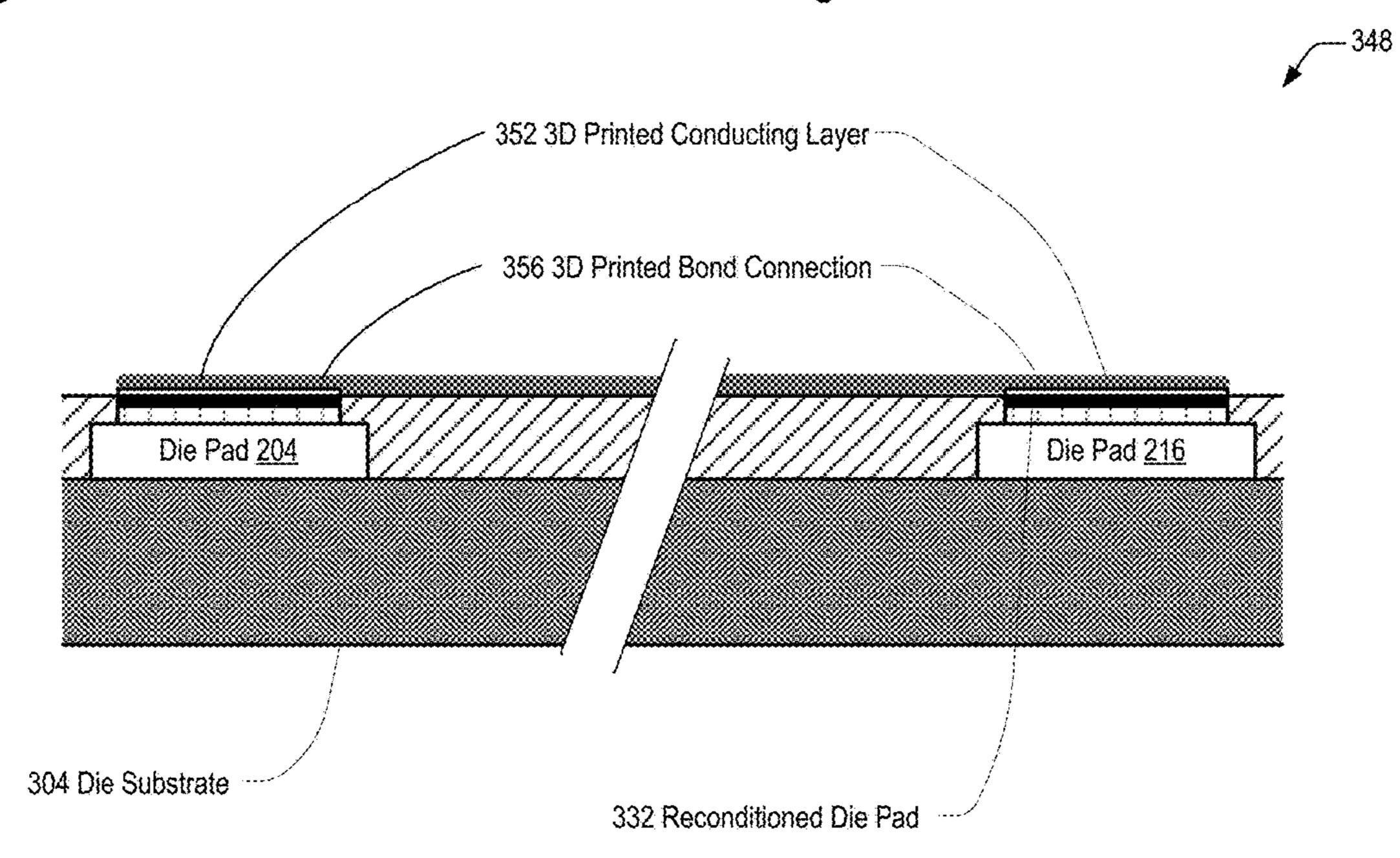

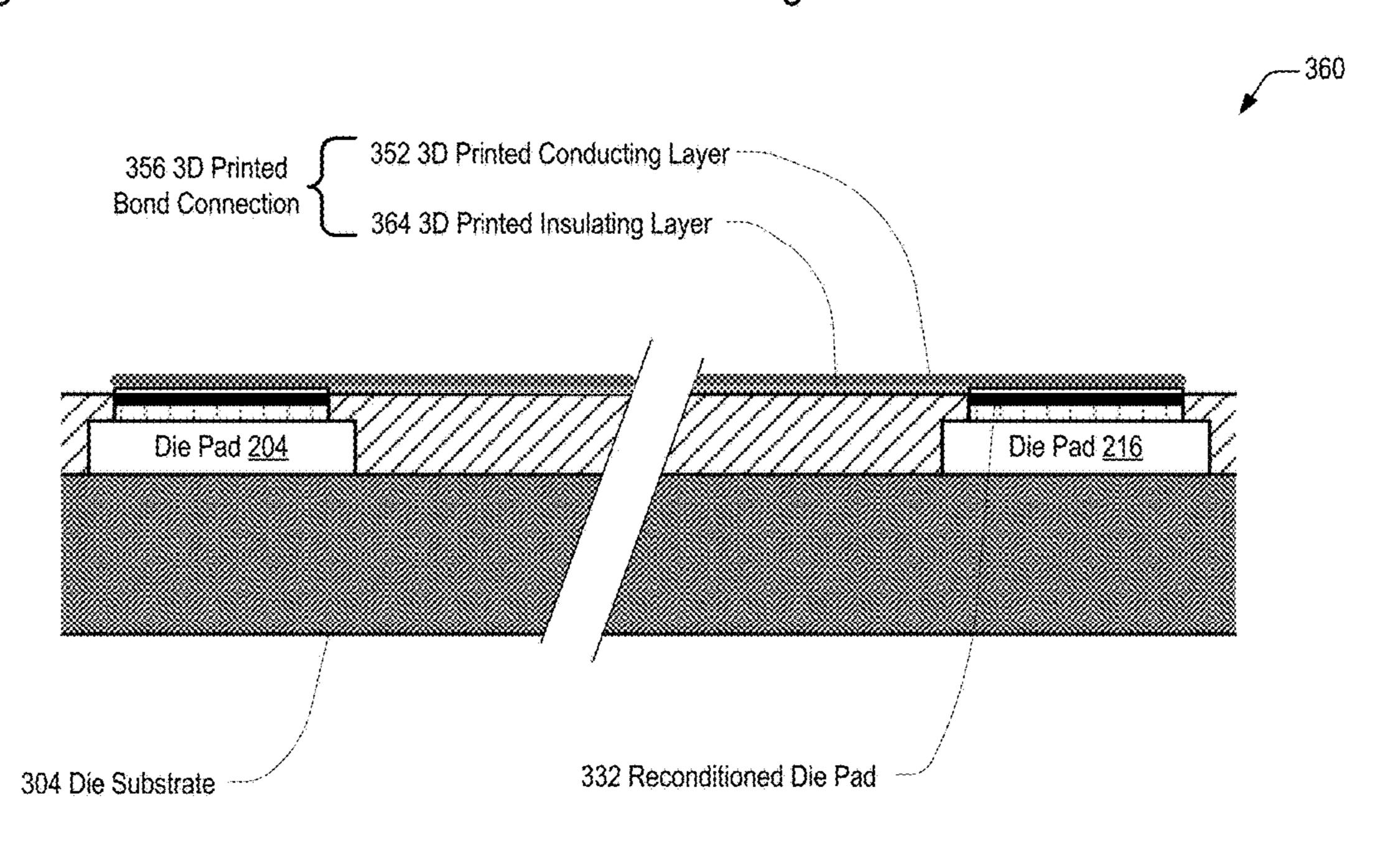

- FIG. 3H is a diagram illustrating a section A-A of a reconditioned die after a 3D printing process in accordance with a second embodiment of the present invention.

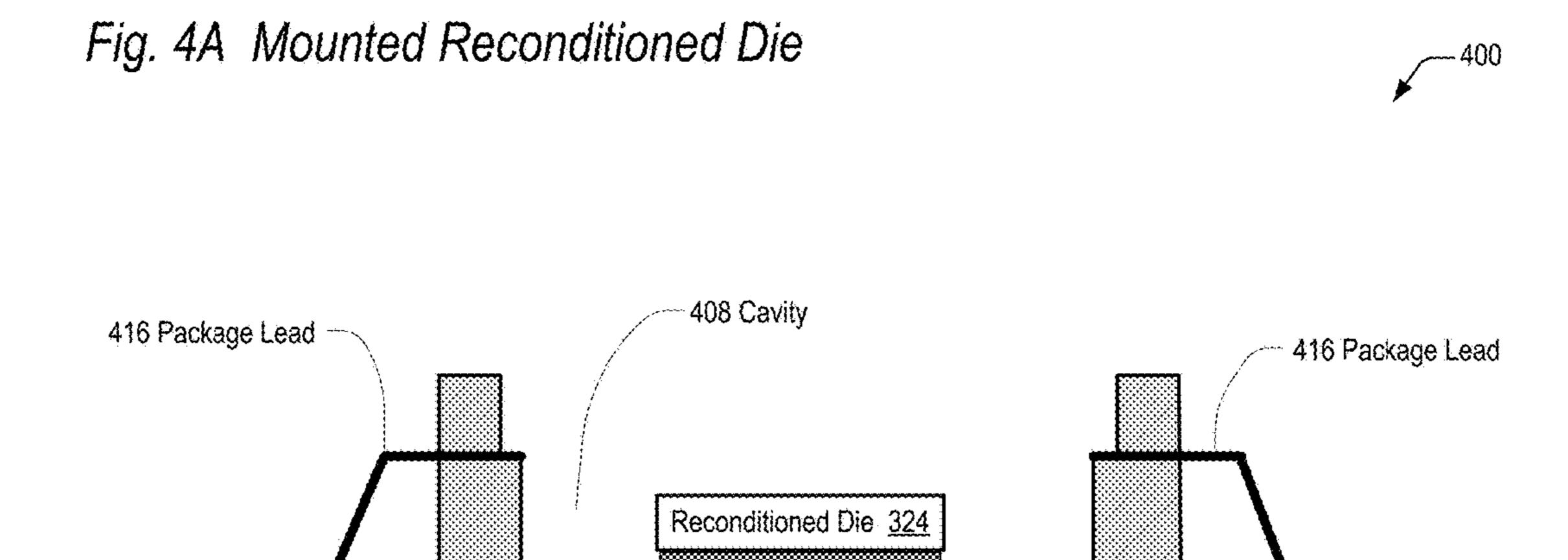

- FIG. 4A is a diagram illustrating a mounted reconditioned die in accordance with embodiments of the present inven- 45 molten metal. tion.

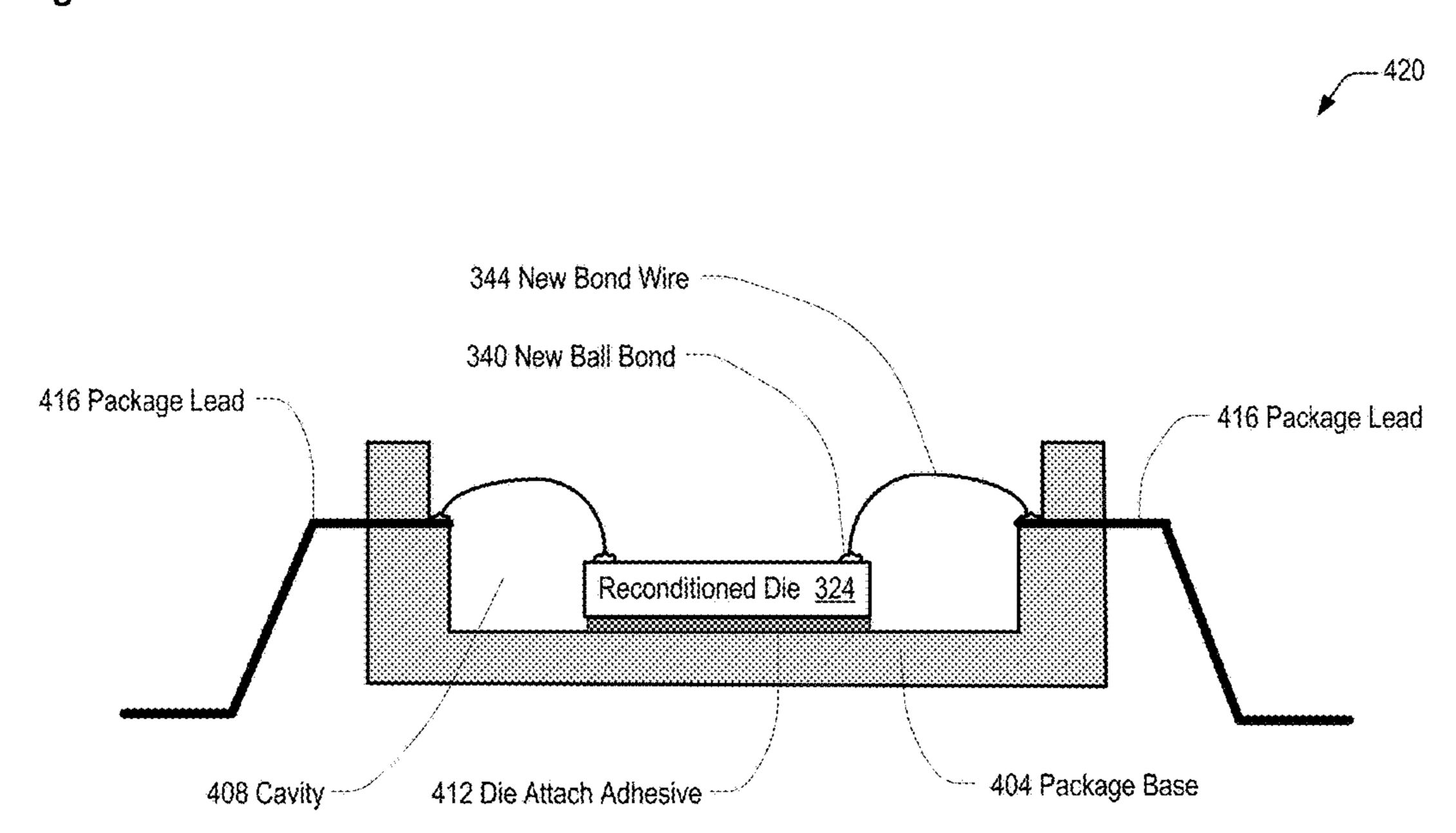

- FIG. 4B is a diagram illustrating a rebonded reconditioned die with new bond wires in accordance with a first embodiment of the present invention.

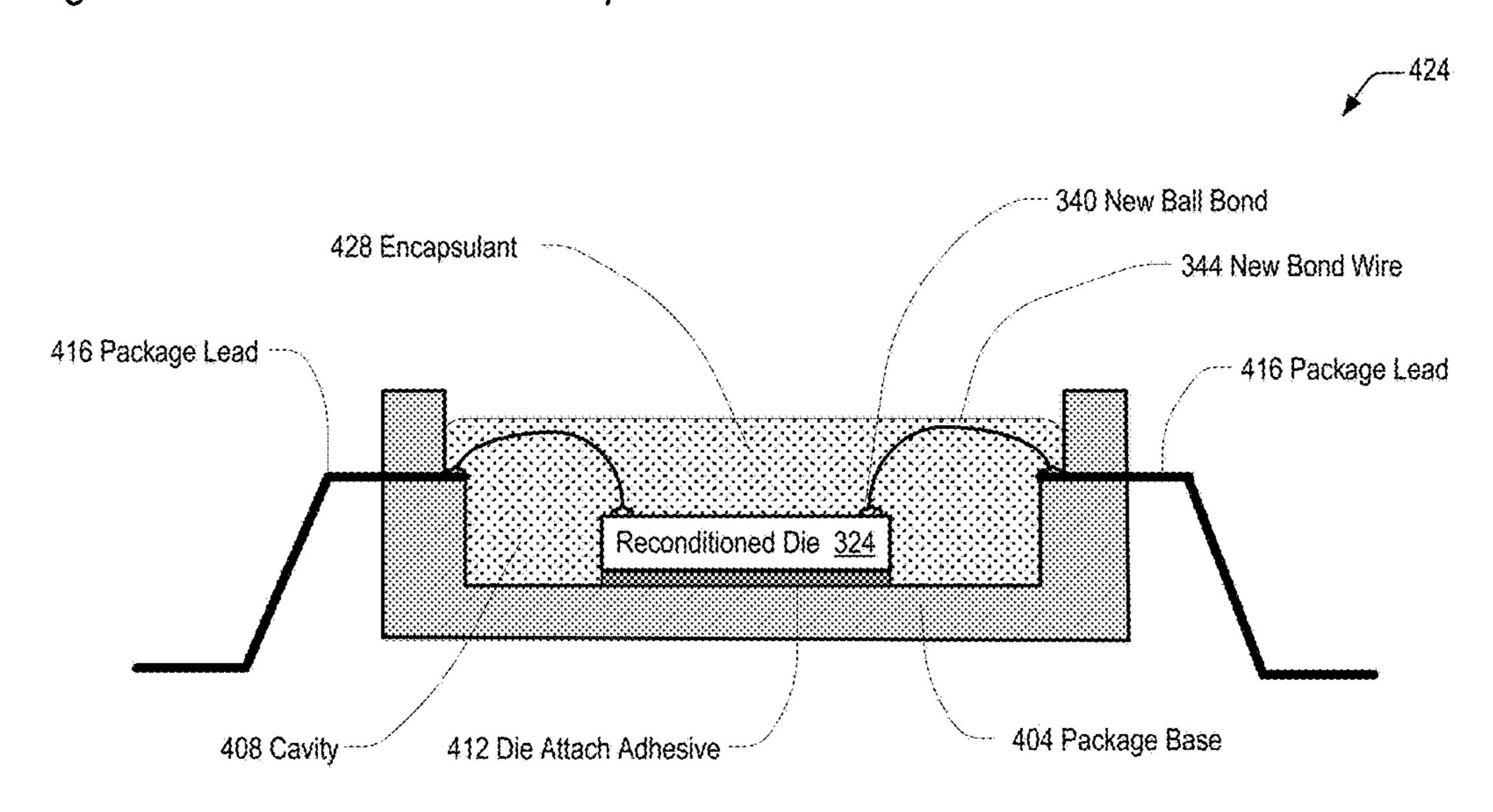

- FIG. 4C is a diagram illustrating a rebonded and encap- 50 sulated reconditioned die in accordance with the first embodiment of the present invention.

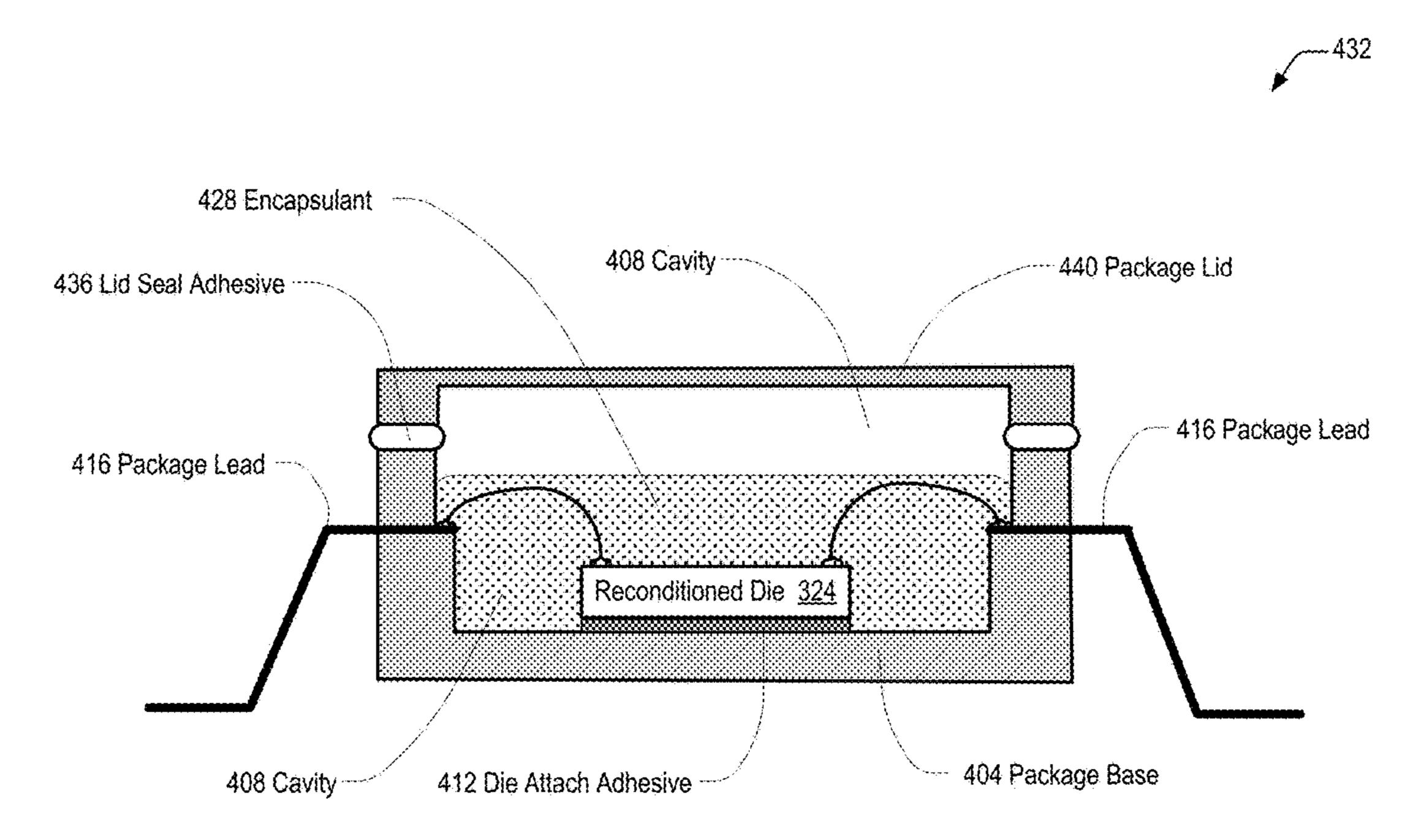

- FIG. 4D is a diagram illustrating a repackaged integrated circuit in accordance with the first embodiment of the present invention.

- FIG. 5A is a diagram illustrating a rebonded reconditioned die with 3D printed bond conductors in accordance with a second embodiment of the present invention.

- FIG. 5B is a diagram illustrating a rebonded and encapsulated reconditioned die in accordance with the second 60 embodiment of the present invention.

- FIG. 5C is a diagram illustrating a repackaged integrated circuit in accordance with the second embodiment of the present invention.

- FIG. 6A is a diagram illustrating a rebonded recondi- 65 tioned die with 3D printed bond insulators in accordance with a third embodiment of the present invention.

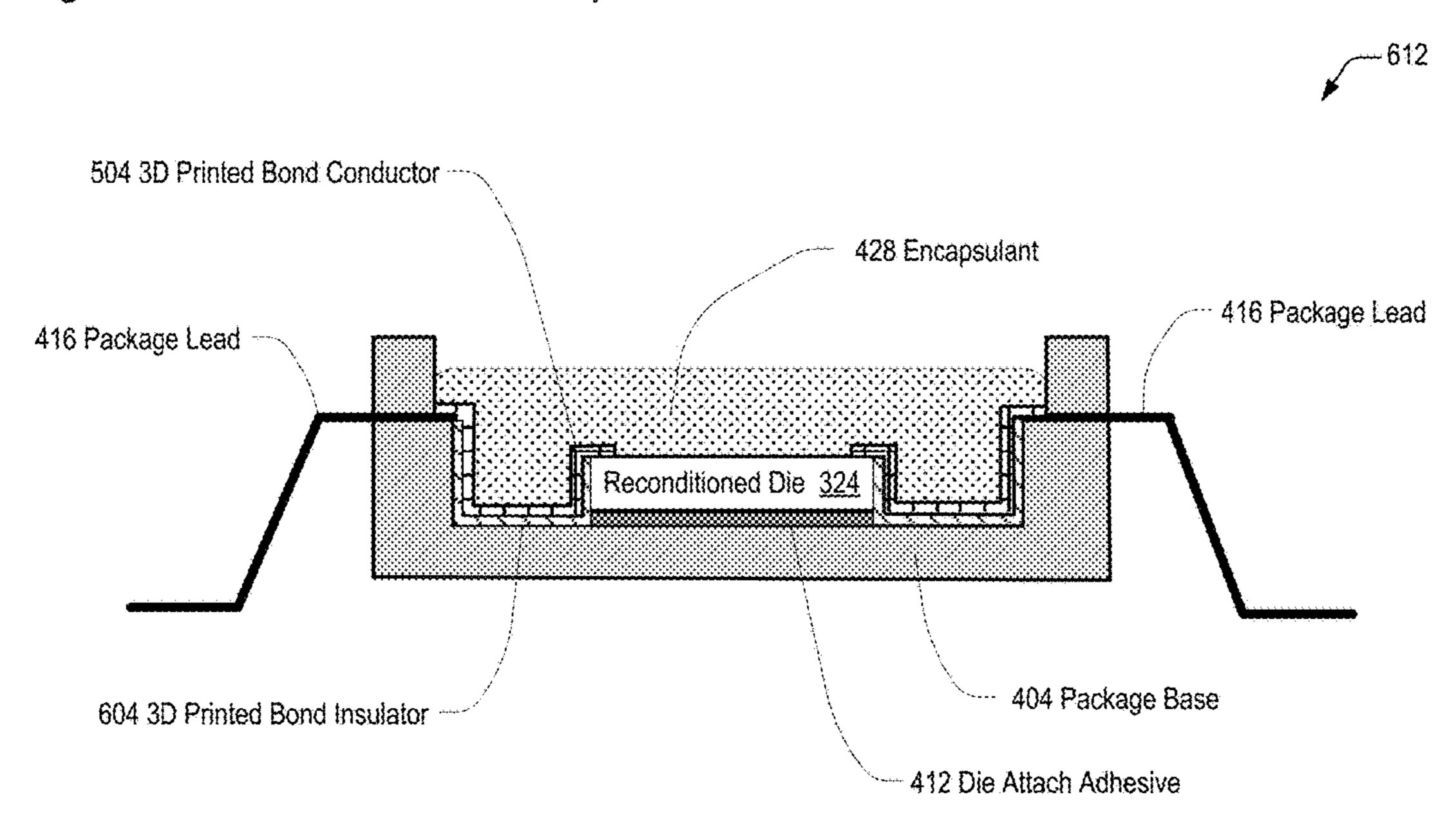

- FIG. 6B is a diagram illustrating a rebonded reconditioned die with 3D printed bond conductors over 3D printed bond insulators in accordance with the third embodiment of the present invention.

- FIG. 6C is a diagram illustrating a rebonded and encapsulated reconditioned die in accordance with the third embodiment of the present invention.

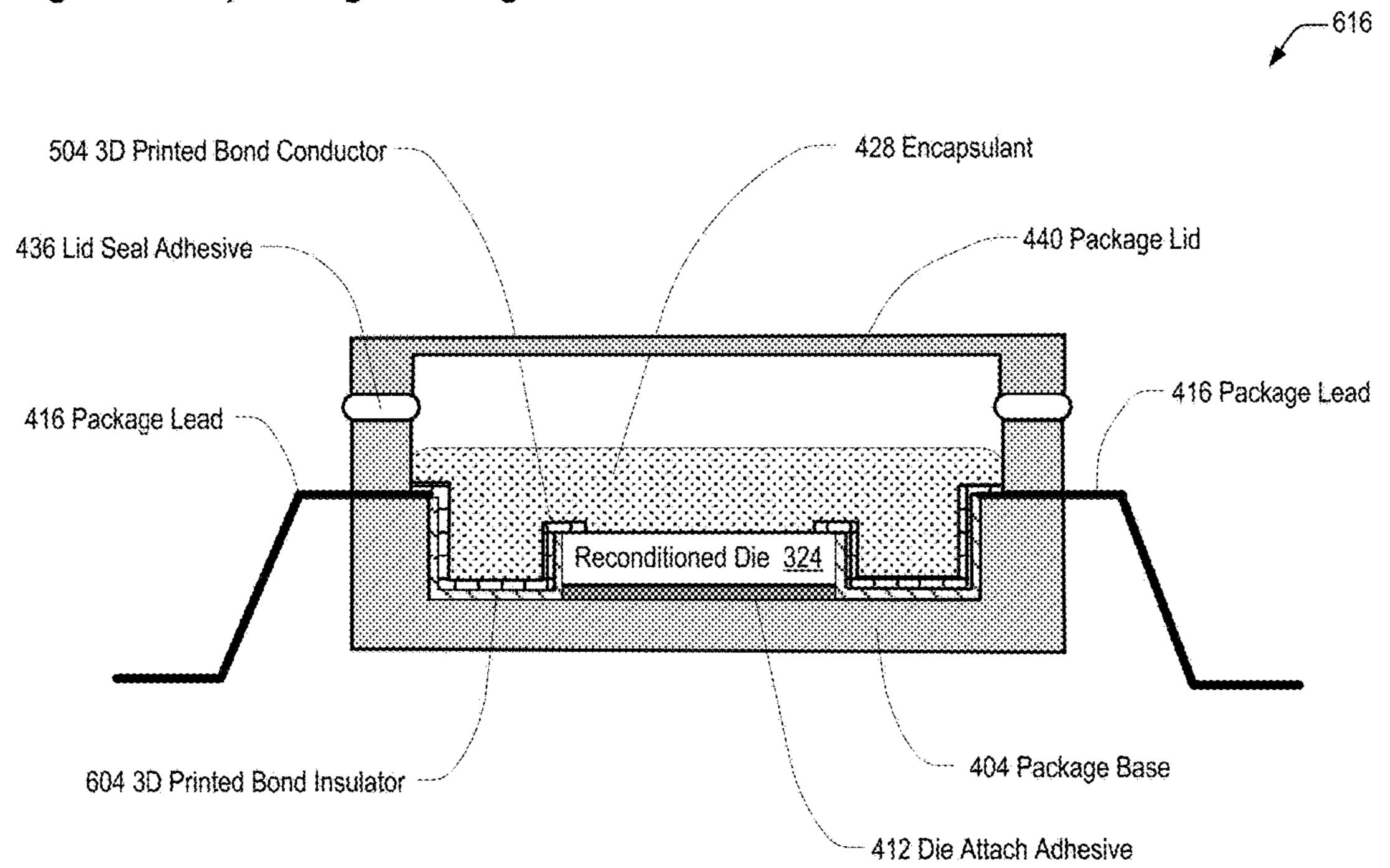

- FIG. **6**D is a diagram illustrating a repackaged integrated circuit in accordance with the third embodiment of the 10 present invention.

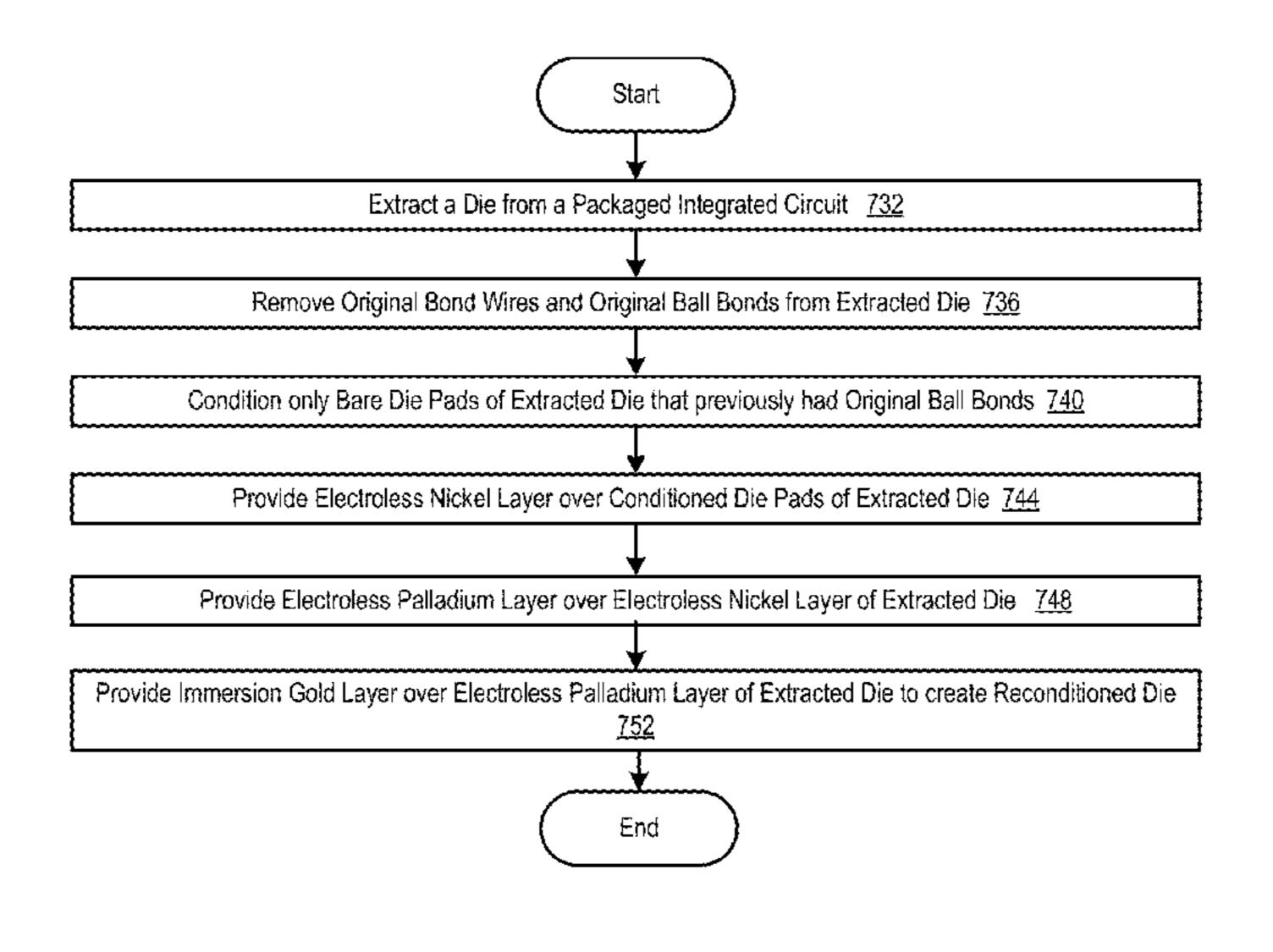

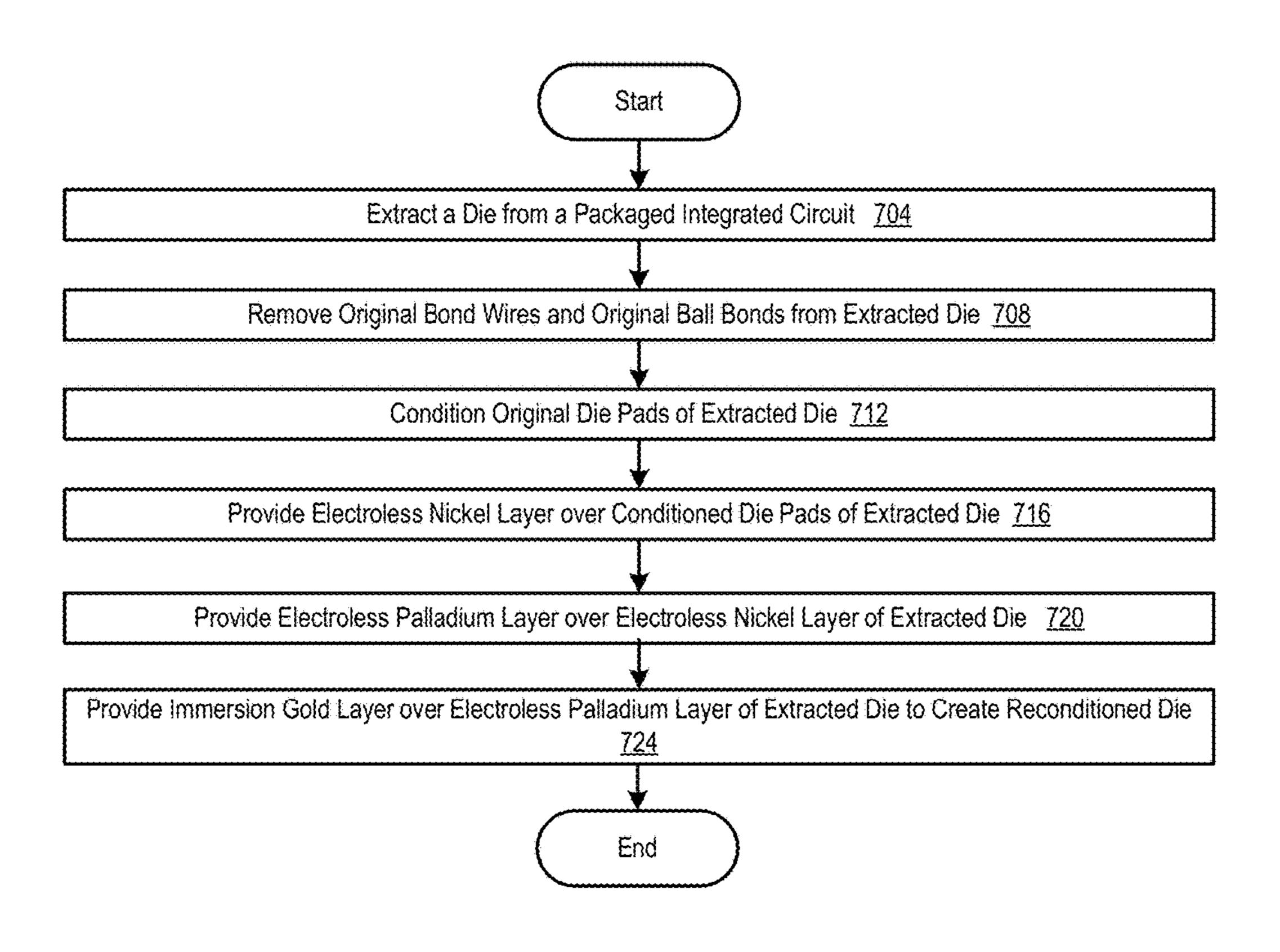

- FIG. 7A is a flowchart illustrating a reconditioning process for an extracted die in accordance with an embodiment of the present invention.

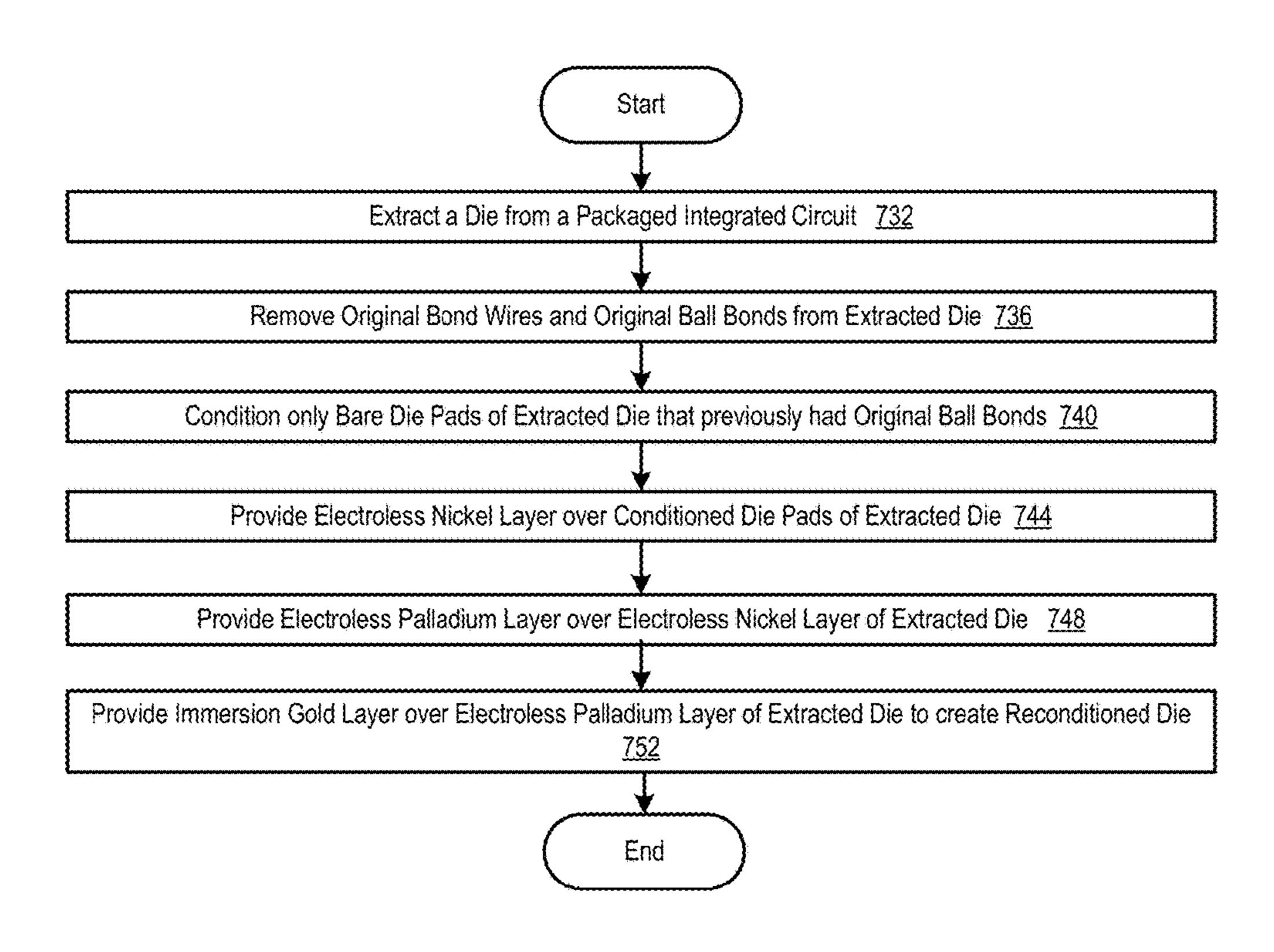

- FIG. 7B is a flowchart illustrating a reconditioning pro-15 cess for an extracted die in accordance with another embodiment of the present invention.

- FIG. 8 is a diagram illustrating applying insulating and conducting material by a 3D printer in accordance with embodiments of the present invention.

- FIG. 9A is a flowchart illustrating an assembly process for a repackaged integrated circuit in accordance with embodiments of the present invention.

- FIG. 9B is a flowchart illustrating an assembly process for a repackaged integrated circuit in accordance with other 25 embodiments of the present invention.

- FIG. 10 is a flowchart illustrating a vacuum bake process in accordance with embodiments of the present invention.

#### DETAILED DESCRIPTION

Many operating environments require integrated circuit components capable of operating reliably at extended temperatures. Some of these environments include engine controls, down-hole drilling, and foundry manufacturing opera-FIG. 3F is a diagram illustrating a section A-A of a 35 tions. Engine controls are often located in close proximity to an internal combustion, gas turbine, or jet engine, and are sometimes located on the engine side of a firewall. Downhole drilling requires a wide variety of sensors, control components, and communication components operating in 40 close proximity to a drill. In addition to heat generated by the drill itself, drilling far below the Earth's crust can reach operating environment temperatures of greater than 200° C. due to geothermal heat. Foundry operations require sensors and control components operating in close proximity to

> Although military grade integrated circuits are often desirable for extended high temperature environments, in many cases the environments themselves experience higher temperatures than the military grade integrated circuit temperature rating. For example, down-hole drilling environments sometimes reach temperatures of 250° C., while military-grade integrated circuits commonly have a -55° C. to 125° C. operating temperature range. Another problem is the required integrated circuits may not be available in 55 packages that can reliably withstand these temperature extremes. Required integrated circuits are sometimes out of production, and it is typically prohibitively expensive to procure new integrated circuits in suitable packaging.

In some environments, traditional ceramic or metal hermetic packaging may be unsuitable for target environments. For example, a target environment may be sufficiently compact and space-constrained that traditional hermetic packaged integrated circuits may not fit within a required envelope. Or, the target environment may experience very high or unpredictable levels of shock and vibration that may render traditional integrated circuits using ball bonds and wire bonds potentially unreliable. Therefore, what is needed

are methods and assemblies for creating repackaged integrated circuits able to work reliably within extended temperature operating environments.

Referring now to FIG. 1, a diagram illustrating a bare die 100 with original die pads 104 in accordance with embodiments of the present invention is shown. Bare die 100 is an individual semiconductor die or substrate, and is usually fabricated in suitable technologies including Silicon (Si) and Gallium Arsenide (GaAs). Bare die 100 may have a single die or multiple interconnected dice. Regardless whether bare 10 die 100 includes a single die or multiple interconnected dice, die circuitry is connected to original die pads 104 of the bare die 100. Original die pads 104 are generally aluminum (Al) or copper (Cu) alloy pads. Section A-A provides a reference to an end-on view for other drawings to illustrate the 15 ments of the present invention is shown. A modified construction and methods of the present invention. Bare die 100 is assumed to be a new production die, and not previously packaged.

Referring now to FIG. 2, a diagram illustrating an extracted die 200 with die pads, ball bonds, and bond wires 20 in accordance with embodiments of the present invention is shown. An extracted die 200 is a fully functional semiconductor die removed from a previous integrated circuit package. In most embodiments, extracted die 200 is an individual semiconductor die or substrate, and is usually fabricated in 25 suitable technologies including Silicon (Si) and Gallium Arsenide (GaAs). Extracted die 200 may have a single die or multiple interconnected dice. Regardless whether extracted die 200 includes a single die or multiple interconnected dice, die circuitry is connected to original die pads 30 204, 216 of the extracted die 200. Original die pads 204 and unbonded die pads 216 are generally aluminum (Al) or copper (Cu) alloy pads. Each previously used original die pad 204 of the extracted die 200 has an original ball bond **208** present (usually gold), and possibly an associated original bond wire **212**. However, in many cases all original bond wires 212 have been removed from original ball bonds 208 as part of a die extraction process. When the extracted die 200 was present in whatever previous package was used for the extracted die 200, original bond wires 212 connected 40 each of the original gold ball bonds 208 to a lead or a downbond of the previous package. FIG. 2 illustrates an exemplary extracted die 200, after it has been removed from a previous package. Therefore, some original bond wires 212 have been removed and only original gold ball bonds 45 208 and two original bond wires 212 remain. Depending on the specific extracted die 200, one or more unbonded die pads 216 may be present—where no original ball bond 208 and original bond wire 212 previously existed. Unbonded die pads 216 generally indicate a no connect to the previous 50 package leads, and may or may not be connected to other circuitry of the extracted die 200. Section A-A provides a reference to an end-on view for other drawings to illustrate the construction and methods of the present invention.

A-A of an extracted die 200 in accordance with embodiments of the present invention is shown. FIGS. 3A-3H illustrate a preferred reconditioning process to be applied to at least original die pads 204, and possibly unbonded die pads 216, for an extracted die 200 prior to assembling into 60 a new hermetic assembly. In some embodiments, the processing steps shown in FIGS. 3C-3H may also be applied to original die pads 104 of a bare die 100, as well.

Extracted die 200 includes a die substrate 304 including various metallization layers known in the art. On the surface 65 of the die substrate 304 are one or more die pads 204, 216. A passivation layer 308 is applied over the die substrate 304

in order to protect the circuits of the die substrate 304, and the passivation layer 308 is relieved at each of the original die pads 204, 216 in order to provide bonding access.

Where original ball bonds **208** and/or original bond wires 212 are present on original die pads, the die pads are die pads 204. Where no original ball bonds 208 and/or original bond wires 212 are applied to original die pads, the die pads are die pads 216. FIG. 3A illustrates the point at which the extracted die 200 has been removed from its' original package and one or more original ball bonds 208 and/or original bond wires 212 are present.

Referring now to FIG. 3B, a diagram illustrating a section A-A of a modified extracted die 312 after original ball bond and original bond wire removal in accordance with embodiextracted die 312 is an extracted die 200 with all original ball bonds 208 and original bond wires 212 removed. Although in some embodiments original ball bonds 208 may be removed by mechanical means, in most cases it is preferable to use chemical removal means by known processes. FIG. 3B illustrates an original ball bond 208 and original bond wire 212 removed from the original die pad 204. Not shown in FIG. 3B is that after removing the original ball bond 208 and original bond wire 212, some amount of intermetallic residue may be present on the original die pads 204. This generally requires removal to make sure there are no impurities or residue on the original die pads 204. The residue removal is referred herein as conditioning the die pads 204. Removal is preferably performed using a mild acid wash. The acid wash is followed by an acid rinse that removes surface oxides present on the original die pads 204. For plating on an Aluminum die pad surface, a Zincate process is used to etch away a very fine layer of Aluminum from the die pads 204 and redeposit a layer of Zinc (Zn) on the die pads 204. The fine layer of Zinc will then act as a catalyst for the Nickel plating to follow, as described herein.

Once in a clean and flat state, the original die pads 204 are considered conditioned die pads and are ready to be reconditioned. Reconditioning of the present invention is a process whereby the original die pads 204, and possibly unbonded die pads 216, are built up by successive and ordered application of specific metallic layers prior to secondary wire bonding or 3D printing bond connection processes described herein.

In one embodiment, after an extracted die 200 is removed from a packaged integrated circuit, only original bond wires 212 are removed—thus leaving original ball bonds 208 on original die pads 204 of the extracted die 200. Original ball bonds 208 must be removed prior to reconditioning original die pads 204. Therefore, in some embodiments the metallic layers of the present invention are not provided to unbonded die pads 216, but rather original die pads 204 following original ball bond 208 removal.

Referring now to FIG. 3C, a diagram illustrating a section Referring now to FIG. 3A, a diagram illustrating a section 55 A-A of electroless Nickel layer application in accordance with embodiments of the present invention is shown. Electroless plating is more cost effective than electroplating since it does not require expensive photolithography and etch processes. However, electroless processes generally require thicker metal layers for good bondability. The present application includes both electroless plating and electroplating.

> A Nickel (Ni) layer 316 applied over a conditioned conventional Aluminum (Al) bond pad 204, 216 have been found to protect pad surfaces. Nickel possesses a much higher elastic modulus than either Copper (Cu) or Aluminum (Al), which leads Nickel to have high stiffness and

fracture toughness and resist deflection and absorb energy during bonding processes. Thus, Nickel is a preferred metallic layer 316 for the initial layer application following original die pad 204, 216 conditioning.

An electroless Nickel plating bath is very complex and 5 contains more chemicals (i.e. reducing agents, complexant or chelating agents, stabilizers, etc) than the Nickel source alone. These bath components perform specific functions during the chemical reaction. They are important in order to obtain a good quality Nickel deposit and must be monitored 10 carefully during processing.

The plating rate of Nickel is a controllable parameter during the plating process, which in turn affects the final surface roughness. A fast plating rate will obviously increase the process throughput, but fast plating rates can also result 15 in a rougher Nickel finish. Therefore, a careful balance must be maintained between processing speed and surface quality. If the Nickel surface is too rough, the next successive metal layers to be plated over the Nickel (i.e. Palladium and Gold) will follow the contours and also result in a rougher surface. 20 Both surface hardness and roughness have a strong effect on wire bondability and bond strength. Harder and rougher surfaces are typically less bondable. For wire bonding applications, the electroless Nickel layer 316 is generally 120-240 microinches thick. However, since the processes of 25 the present application alternatively apply 3D printed bond connections 356 to the reconditioned die pads 332, a rougher Nickel layer 316 may be preferable for those embodiments to aid in adhesion since conventional wire bonds are not utilized. Thus, a faster Nickel plating **316** process may not 30 only be preferable for application of subsequent layers including 3D printed bond connections **356**, it also increases production throughput for reconditioned die pads 332.

Referring now to FIG. 3D, a diagram illustrating a section A-A of electroless Palladium layer 320 application in accordance with embodiments of the present invention is shown. Electroless Palladium (Pd) 320 is applied over the electroless Nickel (Ni) 316 layer of FIG. 3C in order to inhibit Nickel diffusion into the immersion gold layer 328 applied afterward.

Palladium plating 320 was first investigated as a replacement for purely gold plating in order to alleviate the high cost of gold plating. Palladium and Palladium-Nickel alloys were initially developed for contact wear resistance in electrical connector applications, but other technical advan- 45 tages were identified as usage grew. Not only is a pure Palladium layer 320 very hard, but it is also very dense, which assists as a diffusion barrier. As with the electroless Nickel layer 316, the electroless Palladium layer 320 requires a catalyst pretreatment to prepare the surface for 50 deposition. The metal source is typically a Palladium-Ammonia compound with a hydrazine reducing agent for metal deposition. For wire bonding applications, the electroless Palladium layer 320 is generally 2-4 microinches thick, approximately 2 orders of magnitude thinner than the elec- 55 troless Nickel layer **316**. Similar thicknesses may be used for 3D printed bond connections **356**.

Referring now to FIG. 3E, a diagram illustrating a section A-A of immersion Gold layer 328 application in accordance with embodiments of the present invention is shown. The 60 immersion Gold layer 328 is applied over the electroless Palladium layer 320, and provides the top layer of the reconditioned die pads 332. Gold has long been a mature plating process for semiconductor applications. Two types of Gold plating processes through chemical reactions are used 65 today: immersion and autocatalytic. Immersion Gold plating 328 is a self-limiting galvanic displacement process, where

8

no reducing agent is required. For wire bonding applications, the electroless Gold layer 328 is generally at least 1-2 microinches thick, and preferably thicker. Similar thicknesses of 1-2 microinches thick may be used for 3D printed bond connections 356. Following the process step of FIG. 3E, the die is a reconditioned die 324. A bare die 100 may also be processed as shown in FIGS. 3C-3F, but does not require the processing steps shown in FIGS. 3A and 3B due to the absence of ball bonds 208, oxides, and other residues or metallic impurities present on original die pads 104.

Because the plating process described herein uses gold as the bonding layer with gold bond wire 344 or 3D printed bond connections 356, there is no Aluminum (Al)-Gold (Au) interface that can degrade and corrode. Thus, the plating process produces more reliable bonding interfaces and is preferred for high temperature and hermetic applications over previous processes that maintained Al—Au interfaces and utilize moisture getter, noble gas insertion, and vacuum bakes to purge moisture from integrated circuit packages.

Referring now to FIG. 3F, a diagram illustrating a section A-A of a reconditioned die after a new ball bonding process 336 in accordance with embodiments of the present invention is shown. The combination of the electroless Nickel layer 316, electroless Palladium layer 320, and the immersion Gold layer 328 produces reconditioned die pads 332. Once die pads 204, 216 have been reconditioned, the reconditioned die **324** is secured within a new package. A suitable die attach adhesive 412 or similar compound secures the reconditioned die 324 within a cavity 408 of a new package base 404. Once secured, new ball bonds 340 and new bond wires 344 are provided between the reconditioned die pads 332 and either package leads 416 or downbonds, as required. New ball bonds 340 and new bond wires 344 may be provided to both original die pads 204 (i.e. where an original ball bond 208 previously existed) or to previously unbonded die pads 216, depending on the desired functionality. The processing shown in FIG. 3F is before encapsulant 428 is introduced, or performing lid seal operations.

Referring now to FIG. 3G, a diagram illustrating a section 40 A-A of a reconditioned die after a 3D printing process 348 in accordance with a first embodiment of the present invention is shown. In some embodiments, rather than applying conventional ball bonds 340 and bond wires 344 as shown in FIG. 3F, it may be preferable to 3D print a bond connection 356 instead. In the illustrated embodiment, the 3D printed bond connection **356** is a 3D printed conducting layer 352. Once die pads 204, 216 have been reconditioned, a 3D printer applies 3D printed bond connections 356 as described herein. 3D Printed conducting layer **352** thickness can be less than 2 microns and is preferably 0.5-1 microns The embodiment shown in FIG. 3G is suitable where there are only non-conductive surfaces between reconditioned die pads 332 and package leads 416 or downbonds. For example, if a new package base 404, die attach adhesive 412, and non-die pad 332 surfaces of the reconditioned die **324** are non-conductive, then 3D printed conducting layers **352** are appropriate by themselves. The processing shown in FIG. 3G is before encapsulant 428 is applied, or a lid is sealed to a package base.

Referring now to FIG. 3H, a diagram illustrating a section A-A of a reconditioned die after a 3D printing process 360 in accordance with a second embodiment of the present invention is shown. In other embodiments, rather than applying conventional ball bonds 340 and bond wires 344 as shown in FIG. 3F or only 3D printed conducting layer 352 as shown in FIG. 3G, it may be preferable to include a 3D printed insulating layer 364. In the illustrated embodiment,

the 3D printed bond connection 356 includes both a 3D printed conducting layer 352 and a 3D printed insulating layer **364**. 3D Printed conducting layer **352** and 3D printed insulating layer 364 thickness each can be less than 2 microns and is preferably 0.5-1 microns. Therefore, the 5 preferred thickness of 3D printed bond connections **356** is less than 4 microns total.

Once die pads 204, 216 have been reconditioned, a 3D printer applies 3D printed bond connections 356 as described herein. The embodiment shown in FIG. 3H is 10 suitable where there are conductive surfaces between reconditioned die pads 332 and package leads 416 or downbonds. For example, if a new package base **404** is conductive, then 3D printed insulating layer 364 is first applied over conductive surfaces of the new package base 404 between the 15 reconditioned die pads 332 and package leads 416. Once the 3D printed insulating layer **364** has been applied, a 3D printer applies a 3D printed conducting layer 352 over the 3D printed insulating layer **364**. The 3D printed conducting layer 352 makes electrical contact between a reconditioned 20 die pad 332 and a package lead 416 or downbond, while the 3D printed insulating layer **364** electrically isolates the 3D printed conducting layer 352 from conductive surfaces of the new package base 404. The processing shown in FIG. 3H is before encapsulant 428 is introduced, or performing lid 25 seal operations.

Referring now to FIG. 4A, a diagram illustrating a mounted reconditioned die 400 in accordance with embodiments of the present invention is shown. FIG. 4A illustrates the step immediately following fabrication of the reconditioned die 324 shown in FIG. 3E. The reconditioned die 324 is secured within a cavity 408 of a package base 404 with a die attach adhesive 412. The package base 404 includes any number of package leads 416, which provide electrical contact with other substrates or printed circuit boards. In the 35 preferred embodiment, the package base 404 may be a hermetic package base 404, such as a metal or ceramic package base 404. In other embodiment, the package base 404 may be non-hermetic package base 404. In some embodiments, the die attach adhesive 412 may be a low- 40 halide content die attach adhesive, while in other embodiments the die attach adhesive 412 may be a conventional die attach adhesive **412**. Once in the configuration shown in FIG. 4A, the mounted reconditioned die 400 is ready to be bonded.

Referring now to FIG. 4B, a diagram illustrating a rebonded reconditioned die with new bond wires 420 in accordance with a first embodiment of the present invention is shown. The embodiment illustrated in FIG. 4B shows new bond wires 344 and new ball bonds 340 applied to the 50 printed bond conductors 504 for new bond wires 344 and reconditioned die 324 and package leads 416. Although not specifically illustrated, it should be understood that reconditioned die 324 includes reconditioned die pads 332, to which new bond wires 344 and new ball bonds 340 are attached. The new bond wires **344** may be applied by any 55 known means, including but not limited to thermosonic bonding or wedge bonding. FIG. 4B provides an alternative view to FIG. 3F.

Referring now to FIG. 4C, a diagram illustrating a rebonded and encapsulated reconditioned die 424 in accor- 60 dance with the first embodiment of the present invention is shown. After all required new bond wires 344 and new ball bonds 340 have been provided between reconditioned die pads 332 and package leads 416 or downbonds, an encapsulant compound **428** is applied within the cavity **408**. The 65 encapsulant compound 428 at least partially fills the cavity 408, and in some embodiment fully fills the cavity 408. In

**10**

the preferred embodiment, the encapsulant 428 completely covers all new bond wires 344. In other embodiments, the encapsulant 428 covers at least conductive areas on the top side of the reconditioned die 324, including any guard rings that may be present. In high shock and vibration environments, there may be a possibility of metallic residue flaking off and potentially contaminating the repackaged integrated circuit 432. The encapsulant 428 prevents any such flaking material from contaminating the interior of the repackaged integrated circuit **432**. The rebonded and encapsulated reconditioned die 424 is considered to be an assembled package base 424.

Referring now to FIG. 4D, a diagram illustrating a repackaged integrated circuit 432 in accordance with the first embodiment of the present invention is shown. Following application of the encapsulant 428 to the cavity 408, the assembly at that point is an assembled package base 424. In some embodiments, the assembled package base 424 is vacuum baked according to the process shown in FIG. 10. In other embodiments, the assembled package base 424 is baked according to the process shown in FIG. 10, but no vacuum is applied during the baking process. In yet other embodiments, the assembled package base **424** is not baked or vacuum baked.

Following any bake or vacuum bake process, a package lid 440 is sealed to the package base 404 using a lid seal adhesive 436. In the preferred embodiment, the package base 404 is a hermetic package base 404, the package lid 440 is a hermetic package lid 440, the lid seal 436 is a hermetic solder or other form of hermetic attachment able to prevent contamination of the cavity 408 by outside agents including moisture, and the die attach adhesive 412 may be a lowhalide die attach adhesive 412. A low halide die attach adhesive **412** has less than 10 parts per million (ppm) halide. It has been well established that halogens in a bond interface may degrade bond strength since out-gassed products from adhesives containing halogens rapidly corrode Aluminum metallization in integrated circuits at high temperatures, thus reducing product lifetime. Hermetic packages are generally manufactured from metal, glass, or ceramic materials. In other embodiments, any of the package base 404, the package lid 440, or the lid seal adhesive 436 may be non-hermetic. Following lid seal operations, the integrated circuit is a repackaged integrated circuit 432 and ready for 45 any hermeticity, electrical, or functional tests required.

Referring now to FIG. 5A, a diagram illustrating a rebonded reconditioned die with 3D printed bond conductors 500 in accordance with a second embodiment of the present invention n is shown. This process substitutes 3D new ball bonds **340** of FIGS. **4**B-**4**D.

The process of FIGS. **5**A-**5**C assumes the processing step illustrated in FIG. 4A has been performed. That is, the reconditioned die 324 is secured within a cavity 408 of a package base 404 with a die attach adhesive 412. The process of 5A-5C is preferably used when low-profile and reliable 3D printed bond connections 356 are desired, and there are not conductive surfaces under the 3D printed bond connections 356 (such as a metal cavity 408 within a metal package base 404, for example). The process of FIGS. 5A-5C applies 3D printed bond conductors 504, built from 3D printed conducting layers 352 of FIG. 3G, directly to surfaces of the reconditioned die 324, die attach adhesive 412, and package base 404. 3D printed bond conductors 504 can be less than 2 microns and are preferably 0.5-1 microns, and provide electrical connections between reconditioned die pads 332 and package leads 416 or downbonds. In the

preferred embodiment, 3D printed bond conductors 504 completely cover one or more reconditioned die pads 332 on the reconditioned die 324. Details of the 3D printing process applied to 3D printed bond conductors 504 is shown and described in more detail with reference to FIG. 8. Although not specifically illustrated, it should be understood that reconditioned die 324 includes reconditioned die pads 332, to which 3D printed bond conductors 504 are attached.

Referring now to FIG. 5B, a diagram illustrating a rebonded and encapsulated reconditioned die 508 in accordance with the second embodiment of the present invention is shown. After all required 3D printed bond conductors **504** have been provided between reconditioned die pads 332 and package leads 416 or downbonds, an encapsulant compound 428 is applied within the cavity 408. The encapsulant compound 428 at least partially fills the cavity 408, and in some embodiment fully fills the cavity 408. In the preferred embodiment, the encapsulant **428** completely covers all 3D printed bond conductors 504. In other embodiments, the 20 encapsulant 428 covers at least conductive areas on the top side of the reconditioned die 324, including any guard rings that may be present. In high shock and vibration environments, there may be a possibility of metallic residue flaking off and potentially contaminating the repackaged integrated 25 circuit **512**. The encapsulant **428** prevents any such flaking material from contaminating the interior of the repackaged integrated circuit 512.

Referring now to FIG. 5C, a diagram illustrating a repackaged integrated circuit 512 in accordance with the second 30 embodiment of the present invention is shown. Following application of the encapsulant 428 to the cavity 408, the assembly at that point is considered an assembled package base 508. In some embodiments, the assembled package base 508 is vacuum baked according to the process shown 35 in FIG. 10. In other embodiments, the assembled package base 508 is baked according to the process shown in FIG. 10, but no vacuum is applied during the baking process. In yet other embodiments, the assembled package base 508 is not baked or vacuum baked.

Following any bake or vacuum bake process, a package lid 440 is sealed to the package base 404 using a lid seal adhesive 436. In the preferred embodiment, the package base 404 is a hermetic package base 404, the package lid 440 is a hermetic package lid 440, the lid seal 436 is a hermetic 45 solder, sealing glass, or other form of hermetic attachment able to prevent contamination of the cavity 408 by outside agents including moisture, and the die attach adhesive 412 may be a low-halide die attach adhesive **412**. A low halide die attach adhesive **412** has less than 10 parts per million 50 (ppm) halide. It has been well established that halogens in a bond interface may degrade bond strength since out-gassed products from adhesives containing halogens rapidly corrode Aluminum metallization in integrated circuits at high temperatures, thus reducing product lifetime. Hermetic 55 packages are generally manufactured from metal, glass, or ceramic materials. In other embodiments, any of the package base 404, the package lid 440, or the lid seal adhesive 436 may be non-hermetic. Following lid seal operations, the integrated circuit is a repackaged integrated circuit **512** and 60 ready for any hermeticity, electrical, or functional tests required.

Referring now to FIG. **6A**, a diagram illustrating a rebonded reconditioned die with 3D printed bond insulators **600** in accordance with a third embodiment of the present 65 invention is shown. This process substitutes 3D printed bond insulators **604** and 3D printed bond conductors **504** for new

12

bond wires 344 and new ball bonds 340 of FIGS. 4B-4D, and adds 3D printed bond insulators 604 to the process shown in FIGS. 5A-5C.

The process of FIGS. 6A-6D assumes the processing step illustrated in FIG. 4A has been performed. That is, the reconditioned die 324 is secured within a cavity 408 of a package base 404 with a die attach adhesive 412. The process of 6A-6D is preferably used when low-profile and reliable 3D printed bond connections **356** are desired, and there are at least some conductive surfaces under the 3D printed bond connections 356 (such as a metal cavity 408) within a metal package base 404, for example). The process of FIGS. 6A-6D applies 3D printed bond insulators 604 and 3D printed bond conductors 504, built from 3D printed insulating layers **364** and 3D printed conducting layers **352**, respectively, of FIG. 3H, directly to surfaces of the reconditioned die 324, die attach adhesive 412, and package base 404. 3D printed bond conductors 504 provide electrical connections between reconditioned die pads 332 and package leads 416 or downbonds. Details of the 3D printing process to apply 3D printed bond insulators 604 and 3D printed bond conductors 504 are shown and described in more detail with reference to FIG. 8. Although not specifically illustrated, it should be understood that reconditioned die 324 includes reconditioned die pads 332, to which 3D printed bond conductors **504** are attached.

Referring now to FIG. 6B, a diagram illustrating a rebonded reconditioned die with 3D printed bond conductors over 3D printed bond insulators 608 in accordance with the third embodiment of the present invention n is shown. After all initial 3D printed bond insulators 604 are 3D printed to surfaces of the reconditioned die 324, package base 404, and die attach adhesive 412, 3D printed bond conductors 504 are printed over the 3D printed bond insulators 604 and between the reconditioned die pads 332 and the package leads 416 or downbonds. 3D Printed bond insulators 604 and 3D printed bond conductors 504 thickness each can be less than 2 microns and is preferably 0.5-1 microns. In the preferred embodiment, 3D printed bond conductors 504 completely cover one or more reconditioned die pads 332 on the reconditioned die 324.

One of the advantages of 3D printing bond insulators 604 and bond conductors 504 is that reliable connections may be obtained by "crossing" 3D printed bond conductors 504. As is well known in the art, crossing new bond wires 344 is at least discouraged, if not forbidden, in many types of integrated circuit packages including military integrated circuits. The reason is that high shock and vibration environments may cause bond wires 344 to move slightly, which may result in short circuits and various forms of malfunction. Because 3D printed bond insulators 604 and conductors 504 are attached directly to underlying surfaces and therefore have no "free mass", they are not at risk of movement during high shock or vibration events. This then allows 3D printed bond connections to be crossed.

For example, for a non-conductive package base 404 and where underlying electrical conduction is not an issue, first 3D printed bond conductors 504 may be 3D printed as shown in FIG. 5A. After that, 3D printed bond insulators 604 may be 3D printed over ("crossing") the first 3D printed bond conductors 504. Following that, second 3D printed bond conductors 504 may be printed directly over the 3D printed bond insulators 604. In fact, several layers of such "crossings" may be performed by repeating this process for third, fourth, etc 3D printed bond conductors. As another example, for a conductive package base 404 where underlying electrical conduction is an issue, first 3D printed bond

insulators 604 may be 3D printed as shown in FIG. 6A. Then, first 3D printed bond conductors **504** may be 3D printed over the first 3D printed bond insulators 604 as shown in FIG. 6B. After that, second 3D printed bond insulators **604** may be 3D printed over ("crossing") the first 5 3D printed bond conductors **504**. Following that, second 3D printed bond conductors 504 may be 3D printed directly over the second 3D printed bond insulators 604. In fact, several layers of such "crossings" may be performed by repeating this process for third, fourth, etc 3D printed bond 10 insulators 604 and 3D printed bond conductors 504.

Referring now to FIG. 6C, a diagram illustrating a rebonded and encapsulated reconditioned die 612 in accordance with the third embodiment of the present invention is shown. After all required 3D printed bond insulators **604** and 15 3D printed bond conductors 504 have been provided between reconditioned die pads 332 and package leads 416 or downbonds, an encapsulant compound 428 is applied within the cavity 408. The encapsulant compound 428 at least partially fills the cavity 408, and in some embodiment 20 fully fills the cavity 408. In the preferred embodiment, the encapsulant 428 completely covers all 3D printed bond insulators 604 and 3D printed bond conductors 504. In other embodiments, the encapsulant 428 covers at least conductive areas on the top side of the reconditioned die 324, 25 including any guard rings that may be present. In high shock and vibration environments, there may be a possibility of metallic residue flaking off and potentially contaminating the repackaged integrated circuit 616. The encapsulant 428 prevents any such flaking material from contaminating the 30 interior of the repackaged integrated circuit 616.

Referring now to FIG. 6D, a diagram illustrating a repackaged integrated circuit 616 in accordance with the third embodiment of the present invention is shown. Following application of the encapsulant 428 to the cavity 408, the 35 respect to FIG. 3D. Flow proceeds to block 724. assembly at that point is considered an assembled package base 612. In some embodiments, the assembled package base 612 is vacuum baked according to the process shown in FIG. 10. In other embodiments, the assembled package base **612** is baked according to the process shown in FIG. **10**, 40 but no vacuum is applied during the baking process. In yet other embodiments, the assembled package base 612 is not baked or vacuum baked.

Following any bake or vacuum bake process, a package lid 440 is sealed to the package base 404 using a lid seal 45 adhesive **436**. In the preferred embodiment, the package base 404 is a hermetic package base 404, the package lid 440 is a hermetic package lid 440, the lid seal 436 is a hermetic solder, sealing glass, or other form of hermetic attachment able to prevent contamination of the cavity 408 by outside 50 agents including moisture, and the die attach adhesive 412 may be a low-halide die attach adhesive **412**. A low halide die attach adhesive **412** has less than 10 parts per million (ppm) halide. It has been well established that halogens in a bond interface may degrade bond strength since out-gassed 55 products from adhesives containing halogens rapidly corrode Aluminum metallization in integrated circuits at high temperatures, thus reducing product lifetime. Hermetic packages are generally manufactured from metal, glass, or ceramic materials. In other embodiments, any of the package 60 base 404, the package lid 440, or the lid seal adhesive 436 may be non-hermetic. Following lid seal operations, the integrated circuit is a repackaged integrated circuit 616 and ready for any hermeticity, electrical, or functional tests required.

Referring now to FIG. 7A, a flowchart illustrating a reconditioning process for an extracted die 200 in accor14

dance with an embodiment of the present invention is shown. Although the process is shown specifically for an extracted die 200, it should be understood that the reconditioning process may also be applied to original die pads 104 of a bare die 100. Flow begins at block 704.

At block 704, a die is extracted (extracted die 200) from a packaged integrated circuit. The extracted die 200 is a fully-functional die and is shown and described in more detail with reference to FIG. 2.

At block 708, original ball bonds 208 and original bond wires 212 attached to the original ball bonds 208 are removed from the extracted die 200 by known processes. Following removal of the original ball bonds 208 and associated original bond wires 212, some metallic or chemical residues is generally on the surface of each original die pad 204. Flow proceeds to block 712.

At block 712, original die pads 204, 216 are conditioned. Any metallic and/or chemical residues are removed from each of the original die pads 204, 216 in order to prepare the original die pads 204, 216 for addition of metallic layers to create a reconditioned die **324**. Removal of the residues is commonly performed using various acid washes and rinses known in the art, and as previously described. Following removal of the residues and drying the original die pads 204, 216, flow proceeds to block 716.